# Selection of test signals and parametric estimation of susceptibility of integrated circuits to electromagnetic conducted disturbances

Jerzy F. Kolodziejski

### ► To cite this version:

Jerzy F. Kolodziejski. Selection of test signals and parametric estimation of susceptibility of integrated circuits to electromagnetic conducted disturbances. 3rd International Workshop on Electromagnetic Compatibility of Integrated Circuits, Nov 2002, Toulouse, France. pp. 31-34. hal-00517772

## HAL Id: hal-00517772 https://hal.science/hal-00517772

Submitted on 15 Sep 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Selection of test signals and parametric estimation of susceptibility of integrated circuits to electromagnetic conducted disturbances

Jerzy F.Kołodziejski Institute of Electron Technology Al. Lotników 32/46 02-668 Warszawa, Poland jekolo@ite.waw.pl

#### Abstract

Some questions related to susceptibility (immunity) of integrated circuits to conducted electromagnetic disturbances are discussed. This includes the selection of test signals, determination of monitoring EMC parameters and proposals of quantitative estimation of integrated circuits susceptibility on the base of measured values of the established parameters and their relative changes under the influence of test signals.

#### Introduction

Some measurement methods of immunity (susceptibility) of integrated circuits (ICs) to electromagnetic disturbances are already available and even applied in the industry, while some others are the subjects of new standard proposals inside IEC. Generally these methods provide qualitative estimation of the properties of tested devices since they are based on the qualitatively formulated malfunction (failure) criteria and alternative classification of the devices subjected to the influence of test signals. The aim of this paper is to turn the attention to the questions, which could extend the use of present methods and to introduce new quantitative estimation of ICs susceptibility properties.

#### Selection of test signals

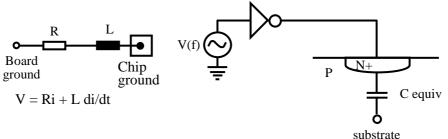

Measurements of influence of conducted disturbances on ICs are performed by applying RF power, voltages or currents to the selected single pin (terminal) or to the set of IC pins. Relevant methods actually considered inside IEC include direct RF power injection DPI, bulk current injection BCI and stimulation of IC placed inside workbench Faraday cage (WBFC method) [9]. Transient disturbances are also expected to be taken into account in the future. Up to now direct RF voltage injection (capacitive coupling) is not considered, although its measuring set-up is similar to that used at DPI and BCI methods. Direct voltage injection is commonly applied in the investigation of digital noise and coupling mechanisms (through the common substrate) in mixed-signal ICs, Fig. 1.

Fig. 1 Illustration of digital noise generation and capacitive coupling in mixed signal ICs

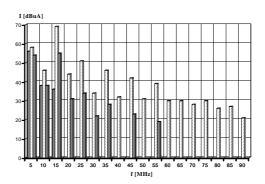

To consider the interference effects of disturbing signals one should take into account the energy carried by disturbances as well as the energy distribution as a function of frequency. Up to now the recommended test signals have the form of sinusoidal continuous waves (CW) or amplitude modulated (AM) waves. These are then the signals that have a fixed frequency or cover only a narrow frequency band. Nevertheless, as results from the experiments, the penetration of disturbing signals significantly depends on the signal waveform, Fig. 2 [4]. Penetration of induced disturbing signal depends of course also on the analysed network of the circuit to which the stimulating signal was applied. Generally the tested network is not known in details but can be characterised by a set of terminal parameters e.g. by "S" or "Z" parameters, if we could measure or simulate them.

Fig.2 Characteristics of penetration of 5 MHz disturbing signal from RESET terminal to supplying line I<sub>SS</sub> for microcontroller 80C31 type; central bar – sinusoidal waveform, left – square waveform, right – triangular waveform

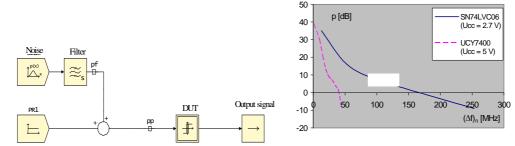

Some investigations were performed in which random signal (white noise) was used to stimulate the tested devices [2]. Signal bandwidth was carefully controlled with the help of sharp filters to monitor an influence of carried energy on the appearance of circuit switching and thus its susceptibility. The relation between the switching threshold and signal bandwidth was clearly pronounced, see Fig. 3.

Fig. 3 Testing of the influence of white noise bandwidth on the level of this signal, required for switching the circuits: a) block diagram of the simulation model, b) results received for two ICs

#### **Monitoring parameters**

It can be assumed that regarding electrical function and physical properties of semiconductor devices we are able to specify electrical parameter (or parameters), which could characterize the device behaviour in the presence of electromagnetic disturbances. They will be called EMC or monitoring parameters. Penetration of external or internal electromagnetic disturbances into the tested devices - discrete elements or integrated circuits, causes a change of the determined parameter (s).

In practice various effects appearing in the ICs are observed under the influence of electromagnetic disturbances. In case of digital circuits the static failure (malfunction) is observed when the disturbance is of sufficient energy to cause a change of the state. At lower disturbance level a propagation delay is usually introduced.

As far as the analogue circuits are concerned the effects of disturbances embrace e.g. changes of amplifier gains, producing of steady state components at the operational amplifiers output, phase shifts, change of reference voltage in band gap voltage reference etc. It results from the above that the susceptibility measurement procedure and conditions as well as acceptance (or rejection) criteria should be individually chosen and specified for IC functional families and even for individual products e.g. voltage regulator [1].

Functional status classification that describes the operational status of IC during and after exposure to an electromagnetic disturbance, as proposed inside IEC immunity standards, seems to be very general and rather suitable for digital ICs.

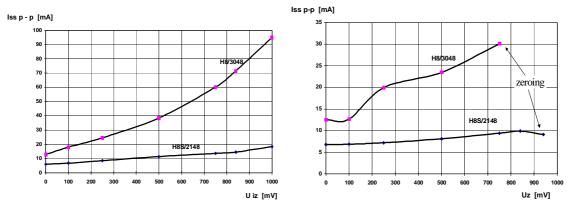

RF component of power supply current can only be proposed as a sufficiently universal parameter indicating the electrical activity of various circuits under the influence of electromagnetic disturbances. Usefulness of this parameter for characterization of electromagnetic emission of ICs has been already accepted, see e.g. [3, 4, 6, 7]. Now it is also shown in some experiments performed for digital circuits [3, 5], that the variable component of power supply currents may be recognised as a good indicator of ICs susceptibility to external electromagnetic disturbances. Changes in disturbance level and terminal to which disturbing signal was applied found their response in the measured variable component of the supply current  $I_{DD}$  or  $I_{SS}$ , Fig. 4.

Fig. 4 Peak-to peak values of supplying current I<sub>SS</sub> as a function of disturbing voltage U<sub>iz</sub> applied to circuits input (left) and RESET (right) for two types of Hitachi microcontrollers

The relative change of the current with respect to the situation without the presence of the disturbances, when we observe current initial value, can thus be proposed as the susceptibility measure. On the basis of measured and registered samples, taken from the supply current, its average value, variance and peak-to-peak values can be calculated through the adequate averaging: coherent for the current function in time domain and non coherent – in frequency domain [8].

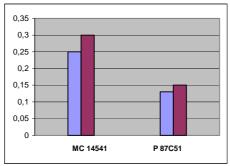

Fig. 5 Average peak-to-peak values of power supply currents for MC 14541 and P87C51 circuits before and after their multiple stimulations

Measurement of RF component of power supply currents can be used to show the "weakening" of the device subjected to the influence of low level disturbance, which is repeated many times. Since the level is low, initially there is no effect in the device functioning. But the physical changes inside the device can be recognised on the base of changes observed in the values of some parameters of supply currents (mainly their peak-to-peak values). The adequate results for multiple ESD were already given in [4]. Changes of supply currents in digital ICs stimulated by the repeated set of fast transients are shown in Fig. 5 [5].

Monitoring parameters can also be determined by using system simulators, if we are able to adequately model the tested IC [1].

#### Basic relations for characterization of relative changes

During the test we can use controlled disturbing signal sources to provide the regulation of disturbance level in continuous or step-by-step manner.

Resulting change of established monitoring parameter X could be expressed in the form

$$\psi(u) = x(u)/x(u=0) = x(u)/x(0)$$

(1)

in which x(0) and x(u) – the values of X parameter of tested device without the presence of disturbances and after the coupling of some disturbances u > 0, respectively.

If we test n devices then we can find n continuous functions

$$\psi_i(u) = x_i(u)/x_i(0)$$

for  $i = 1, 2, ..., n$  (2)

which represent the realizations of random function of relative changes  $\Psi(u)$  of X parameter such that  $P(\Psi(0) = 1) = 1$ . When the disturbing test signal is changed in step-by-step manner then we deal with the function  $\Psi_i(u_i)$

$$\Psi_i(u_j) = x_i(u_j)/x_i(0)$$

for  $i = 1, 2, ..., n; j = 1, 2, ..., k$  (3)

Calculated values represent the observed (experimental) values of random variable  $\Psi(u_j)$  which reflect instantaneous state of the random function of relative changes  $\Psi(u)$  for  $u = u_j$ .

The distribution of random function  $\Psi(u_j)$  can be approximated by normal (Gaussian) distribution, as the result of elimination of the influence of unknown initial distribution of the *X* parameter, obtained through the dividing process. Since that we can assume in practice that nearly all values of random variable  $\Psi(u_j)$  are located inside the interval  $E[\Psi(u_j)] \pm 3\sigma[\Psi(u_j)]$  at which  $E[\Psi(u_j)]$  means the expected value and  $\sigma(\Psi(u_j))$  – standard deviation of random variable  $\Psi(u_j)$ .

Quantitative (parametric) estimation of the device susceptibility (immunity) to electromagnetic disturbances can be done if we would recognize the observed changes of determined EMC parameter as an evidence of a partial failure of the tested device.

Since the values of X parameter are always positive for any  $u_i$ , the following condition is fulfilled

$P[X(u_j) \ge 0] = P[\Psi(u_j) \ge 0] = 1$ We can choose an auxiliary function

(4)

$$\varphi_i(u_j) = \varphi(\psi_i(u_j)) \tag{5}$$

which has the values located inside the interval [0,1].

The values of 0 and 1 can be ascribed to the ultimate states of the tested device, respectively, when it works properly without the presence of any disturbances and when it passes to the malfunction (failure) state. Any intermediate values can be recognised as the probability of partial failure related to the considered X parameter. This approach can be as well useful if we would like e.g. to use combine coefficient embracing more than one monitoring parameter of the tested device.

As an example, the data used to design figure 4 can be taken for calculation. Disturbing signal of 1000 mV caused the increase of  $I_{SS}$  peak-to-peak value for H8/3048 device from initial 12.8 mA to 95 mA. Hence the relative increase is about 7.42. For improved and disturbance "hardened" microcontrollers H8S/2148 the  $I_{SS}$  is generally significantly smaller and increases only about 3 times at the same disturbance level.

Since the interfering effects depend on the energy and frequency of disturbances, the susceptibility features of the IC, determined on the base of relative changes of monitoring parameters, can be generally represented as a surface in 3D space.

#### Conclusion

Any attempt toward generalization of the susceptibility (immunity) determination of different ICs meets many obstacles resulting mainly from the various types of possible disturbances and their levels (reflected by the test severity) as well as from various acceptance or rejection criteria of the tested ICs. In many cases the consideration and use of broadband test signals may be important. The selection and analysis of some monitoring EMC parameters of the ICs allows performing parametric estimation of susceptibility properties of ICs, especially at lower disturbance levels. Among these EMC monitoring parameters the RF component of supply currents seems to be most universal.

#### References

- [1] B.Audone, A.Lamparti: A novel approach to system susceptibility testing. EMC Europe 2000,

- 4<sup>th</sup> European Symposium on EMC Brugge Sept. 11-15, 2000, pp.83-88

- [2] L.Hasse, J.F.Kołodziejski, J.Piasecki, L.Spiralski: EMI of digital circuits. Mechanisms and measurement methods. (In Polish). Elektronika, 2002 Nr. 6, pp. 13-16

- [3] J.F.Kołodziejski, S.Kuciński: Use of power supply currents for electromagnetic compatibility investigation of digital integrated circuits. Proc. of the 16<sup>th</sup> Int. Wrocław Symposium on EMC, 2002 vol. I, pp. 127-132

- [4] J.F.Kołodziejski, S.Kuciński: Comparative study of microcontrollers electromagnetic emission and their immunity. EMC Europe 2000, 4<sup>th</sup> European Symposium on EMC Brugge Sept. 11-15, 2000, pp.335-340

- [5] S.Kuciński: Investigation of digital ICs susceptibility to multiple pulse signals of low energy. (In Polish). Elektronizacja 2002 Nr. 10, pp. 15-18

- [6] Y.Takahata et al.: Power Current Model of IC with Internal Impedance. Technical Report IEICE, EMCJ99-104, Dec. 1999, pp.21-26

- [7] O.Wada et al.: Power Current Model of Digital IC with Internal Impedance for Power Decoupling Simulation. EMC Europe 2000, 4<sup>th</sup> European Symposium on EMC Brugge Sept. 11-15, 2000, pp.315-320

- [8] R.G.Lyons: Understanding digital signal processing. Reading Addison-Wesley 1997

- [9] IEC 62132 Integrated circuits Measurement of electromagnetic immunity, 150 kHz to 1 GHz. Part 1 to 5 (standard proposal).