## Analyse de la robustesse des MOSFET SiC pour les applications diode-less

Oriol Aviño Salvado, Cheng Chen, Cyril Buttay, Hervé Morel, Denis Labrousse, Stéphane Lefebvre, Marwan Ali

#### ▶ To cite this version:

Oriol Aviño Salvado, Cheng Chen, Cyril Buttay, Hervé Morel, Denis Labrousse, et al.. Analyse de la robustesse des MOSFET SiC pour les applications diode-less. Symposium de Génie Electrique (SGE'16), Jun 2016, Grenoble, France. hal-01361711

HAL Id: hal-01361711

https://hal.science/hal-01361711

Submitted on 7 Sep 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Analyse de la robustesse des MOSFET SiC pour les applications « Diode-less »

O. Aviño-Salvado<sup>1</sup>, C. Cheng<sup>1-2</sup>, C. Buttay<sup>1</sup>, H. Morel<sup>1</sup>, D. Labrousse<sup>2</sup>, S. Lefebvre<sup>2</sup>, M. Ali<sup>3</sup>

<sup>1</sup> Univ de Lyon, INSA-Lyon, Lab. Ampère, France

<sup>2</sup> SATIE-ENS Cachan, France

<sup>3</sup> Safran-Tech, Paris-Saclay, France

RESUME – Le carbure de silicium, SiC, présente plusieurs avantages par rapport au silicium pour des applications en électronique de puissance, notamment en termes de faibles pertes. Néanmoins, la maturité technologique n'est pas totalement acquise et des problèmes de fiabilité persistent. Ce papier présente l'étude de l'utilisation des MOSFET SiC sur des applications de type onduleur «diode-less», ainsi que les différents phénomènes associés, parmi lesquels la dégradation de l'oxyde de grille. Plusieurs composants ont été testés et caractérisés périodiquement dans le cas d'un fonctionnement sous conduction inverse. Suite à cette caractérisation, il est observé une dérive de la tension de seuil fortement dépendante du rapport cyclique. Toutefois la jonction P-N ne montre pas de dégradation importante.

Mots-clés—MOSFET, carbure de Silicium (SiC), fiabilité, robustesse, oxyde de grille, tension de seuil, diode intrinsèque, diode-less, pièges.

#### 1. Introduction

Bien que le carbure de silicium soit connu et utilisé depuis plus d'une centaine d'années [1], l'utilisation en tant que semiconducteur est plus récente [2] [3]. Les premières diodes en SiC ont fait leur apparition sur le marché en 2001 [4], et il a fallu attendre 2007 pour l'arrivée des premiers composants JFET, puis 2011 pour les MOSFET.

Parmi les avantages du SiC, son champ électrique de rupture (3-5 MV/cm) est environ dix fois supérieur à celui du Si (0.34 MV/cm). La bande interdite est environ trois fois plus grande pour le SiC (3.26 eV) par rapport au Si (1.11 eV). Les caractéristiques thermiques de la technologie SiC sont aussi supérieures, et le SiC présente une conductivité thermique environ trois fois supérieure (4.9 W/cm·K) au Si (1.5 W/cm·K), ainsi qu'une résistance électrique intrinsèque beaucoup plus faible (0.3 m $\Omega$ ·cm²) par rapport à celle du Si (400 m $\Omega$ ·cm²) à température ambiante et 1200 V de tension de claquage.

Ces caractéristiques font du SiC une technologie très intéressante pour beaucoup d'applications électriques. Il permet une réduction importante des pertes qui, associée à de meilleures performances thermiques, vont minimiser les besoins en refroidissement, et donc le volume global du système de conversion. Ainsi, les meilleures performances à même niveau de tension de blocage permettront l'utilisation des composants de type MOSFET ou JFET SiC dans des applications jusqu'à ce jour réservées aux IGBT silicium telles que les applications ferroviaires ou aéronautiques.

Néanmoins, le développement plutôt lent des composants basés sur la technologie SiC est dû aux défis technologiques sur l'élimination des défauts, tels que des problèmes de dislocation [5], ainsi que des micropipes [6]. Ces défauts ont limité pendant longtemps la capacité de blocage des composants SiC à tension élevée [7], qui est pourtant a priori un point fort de la technologie SiC. De plus, la mobilité dans le canal des MOSFET SiC est limitée à cause des défauts induits par la présence des pièges proches de la bande de conduction [8], et des charges piégées qui réduisent la mobilité par diffusion coulombienne des porteurs dans la couche d'inversion [9].

Bien que les fabricants aient considérablement minimisé ces défauts pour les derniers composants SiC commercialisés, ils ne sont toujours pas totalement maîtrisés et des problèmes persistent [10]. En particulier, on trouve des problèmes de robustesse, tels que les performances sous conditions de court-circuit [11], ainsi que la fiabilité de l'oxyde de grille et la stabilité de la tension de seuil [12, 13], qui restent un des plus importants problèmes de fiabilité des MOSFET SiC [14]. Finalement, la dégradation de la diode interne et donc de la jonction P-N est un des sujets d'étude sur la robustesse des MOSFET SiC [15, 16].

A niveau de la commande, les composants SiC de type BJT ou JFET peuvent avoir besoin d'une circuiterie particulière par rapport aux composants Si [17]. L'une des raisons pour lesquelles le MOSFET SiC est un des composants préférés pour les applications industrielles est la simplicité de son driver, qui reste très proche d'un driver classique de MOSFET Si. Les MOSFET SiC nécessitent une tension négative au blocage (immunité aux dV/dt) et une tension plus élevée que celles des MOSFET Si en régime de conduction (de l'ordre de 20 V).

Dans ce papier, on aborde l'étude de la robustesse de la diode interne des MOSFET SiC sous conditions d'utilisations réalistes dans le contexte de l'aéronautique, donc sous commutation inductive et une tension de 540 V, tension des futurs réseaux HVDC en aéronautique. L'objectif est d'étudier si, avec les composants SiC commercialisés aujourd'hui, il est possible de réaliser des applications « diode-less », pour des onduleurs sans diodes antiparallèles, ce qui permet d'économiser en composants et donc en coût. La dérive de la tension de seuil observée dans la littérature sous conduction inverse [16] a aussi été étudiée, et on évaluera si cela peut avoir une incidence sur la circuiterie de commande.

### 2. ANALYSE DE LA ROBUSTESSE DES MOSFET SIC EN MODE HACHEUR

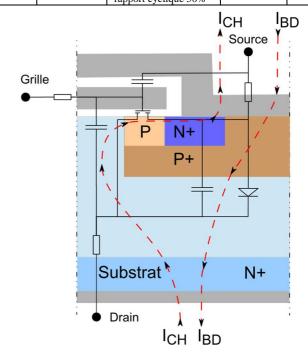

Les MOSFET SiC ont une structure assez semblable à celle des MOSFET Si. La Fig.1 montre la structure typique d'un MOSFET SiC, ainsi que les lignes de courant  $I_{CH}$  quand le courant circule par le canal et  $I_{BD}$  quand il est sollicité par la diode intrinsèque.

Les principaux problèmes de robustesse sur un MOSFET en mode hacheur [16] sont la dérive de la tension de seuil, ainsi que la dégradation de la jonction P-N [18] dans le cas où la diode interne est sollicitée.

Lelis et al. [19] ont montré que l'instabilité de la tension de seuil est liée à l'activation additionnelle de pièges, les « near-interfacial oxide traps », voire à la création de charges d'interface additionnelles qui modifient la tension de seuil. Cette instabilité a été constatée de façon indépendante de la température. On peut donc lier cette problématique à l'injection des porteurs.

Il existe plusieurs phénomènes qui peuvent expliquer l'injection des porteurs dans l'oxyde [20, 21]. Les phénomènes principaux sont : l'effet tunnel, l'injection Fowler-Nordheim et l'injection des porteurs chauds.

Les tests standards JEDEC [22] « High Temperature Gate Bias (HTGB) » et « High Temperature Reverse Bias (HTRB) », voir Tableau 1, sont utilisés pour évaluer la fiabilité des composants, notamment en silicium. Il existe aussi un test « High Temperature Gate Switching (HTGS) » qui est aussi utilisé [23, 13]. Il faut cependant noter que ce test n'est pas un test standard JEDEC.

Des études récentes [13], ont montré une importante dérive de la tension de seuil sur un test HTGB avec des composants excités avec  $V_{GS}$ =20 V. Dans le cas des tests HTRB, la tension de seuil des composants est plus stable [12]. Il est aussi montré [13] que dans le cas d'un test HTGS à excitation pulsée  $V_{GS}$ =+20/-5 V, la dérive de la tension de seuil  $V_{TH}$  est plus faible. Il apparait donc qu'une commande dynamique a des effets différents des conditions statiques telles qu'utilisées dans les tests JEDEC.

Le problème de robustesse de la jonction P-N, qui se dégrade dans le cas où la diode interne est sollicitée, est attribué à la formation de dislocations dans le plan basal. Par conséquent, il faut améliorer l'épitaxie afin de résoudre cette problématique [24, 25].

Aujourd'hui, une solution utilisée pour éviter la dégradation de la jonction P-N est l'utilisation des diodes Schottky en antiparallèle. Cette solution, qui a aussi comme avantages un temps de récupération plus faible, ainsi qu'une possible minimisation des pertes de conduction de la diode, permet d'éviter la dégradation de la diode interne. Néanmoins, c'est une solution qui a un coût important en termes de nombre de composants utilisés. Une solution intermédiaire est une structure qui incorpore une diode Schottky dans la même puce que le MOSFET [18].

#### 3. MÉTHODOLOGIE EXPÉRIMENTALE

L'objectif de l'expérience réalisée est d'étudier la dégradation de la jonction P-N, ainsi que la dérive de la tension de seuil  $V_{TH}$  sur des MOSFET SiC. Les composants sous test (DUT) sont sollicités en régime de conduction inverse sous conditions de commutation inductive. Pour réaliser cette expérience, un banc de test CMB (Chopper Mode Bias) a été conçu.

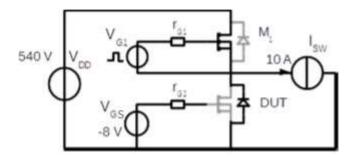

Le banc de test est basé sur une structure « back to back » composée d'un convertisseur abaisseur suivi par un convertisseur élévateur piloté en courant (à une valeur moyenne de 10 A). Cette régulation, fixe aussi le courant sur le convertisseur abaisseur à 10 A, et donc sur le DUT pendant le temps où il est sollicité. La tension de travail est  $V_{\rm DD}$ =540 V. La Fig.2 montre le schéma du convertisseur abaisseur, où la sortie est modélisée comme une source de courant.

Les composants testés sont des transistors MOSFET SiC CREE C2M008012D, 1200 V, 80 m $\Omega$  dans un boîtier TO-247. Les composants sont fixés sur un bloc chauffant avec une régulation de la température conçue pour que la température de jonction soit d'environ 150 °C.

Par la suite, la méthode d'estimation de la température de jonction, ainsi que les différents tests réalisés et les protocoles suivis sont présentés. Les résultats de ces tests seront montrés dans la section suivante.

Tableau 1. Test utilisé sur l'étude de la dérive de la tension seuil  $V_{TH}$

| Acronyme | Test                                     | Conditions du Test                                                                                                                                  | Test<br>Standard     | Test<br>réalisé |

|----------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|

| HTGB     | High<br>Temperature<br>Gate Bias         | $\begin{split} &Ta{=}T_{MAX}\\ &V_{GS}{=}{+}V_{GSMaX}/{-}V_{GSMIN}\\ &ou\ proche.\\ &Tension\ V_{GS}\ constante.\\ &V_{DS}{=}0V \end{split}$        | JESD22<br>A108D      | Non             |

| HTRB     | High<br>Temperature<br>Reverse Bias      | $Ta = T_{MAX}$ $V_{GSMIN} < V_{GS} < 0 \text{ V}$ $V_{DS} = V_{BR} \text{ ou proche}$                                                               | JESD22<br>A108D      | Oui<br>Fig.3    |

| HTGS     | High<br>Temperature<br>Gate<br>Switching | $Ta=T_{MAX} \\ V_{GS}=+V_{GSMaX}/-V_{GSMIN} \\ ou proche. \\ Excitation pulsée. \\ Fréquence et rapport \\ cyclique non \\ determiné. \\ V_{DS}=0V$ | Test non<br>standard | Non             |

| СМВ      | Chopper<br>Mode Bias                     | $Ta=T_{MAX}$ $V_{GS}=-8 \text{ V}$ $V_{DS}=540 \text{ V}$ $f=20 \text{ kHz}$ $rapport cyclique 50\%$                                                | Test non<br>standard | Oui<br>Fig.2    |

Fig.1 Structure interne d'un MOSFET SiC et lignes de courant  $I_{\text{CH}}$  (canal) et  $I_{\text{BD}}$  (diode interne).

Fig.2 Schéma de principe du convertisseur abaisseur du banc de test CMB.

#### 3.1. Estimation de la température de jonction.

L'estimation de la température de jonction a été réalisée en régime stationnaire sur la base de l'équation (1) où  $T_J$  est la température de jonction,  $T_D$  est la température du dissipateur,  $P_D$  représente les pertes dans le composant,  $R_{JB}$  et  $R_{BD}$  sont les résistances thermiques jonction-boîtier, boîtier-dissipateur respectivement.

$$T_{I} = P_{D} \cdot (R_{IB} + R_{RD}) + T_{D} \tag{1}$$

Étant donné que la température du bloc chauffant est contrôlée par un régulateur de température et reste constante, et que la résistance thermique entre jonction et boîtier vaut  $R_{JB}{=}0.65~^{\circ}\text{C}{\cdot}\text{W}$  [26] , il reste à déterminer  $R_{BD}$ .

Pour déterminer la valeur de  $R_{BD},$  un MOSFET a été caractérisé en fonction de la température à un point de travail dans la région de saturation ( $V_{GS}\!\!=\!\!6$  V,  $V_{DS}\!\!=\!\!8$  V) avec incréments de température de 10 °C pour la plage de température comprise entre 60 °C et 150 °C. La courbe caractéristique de  $I_{SAT}$  obtenue, exprimée en Ampères, peut être définie par l'équation (2) . Cette caractérisation a été réalisée avec un traceur Agilent B1505B et un conditionneur thermique Thermonics

T-2500E/300.

$$I_{SAT}(T)\Big|_{\substack{V_{GS}=6V\\V_{DS}}=8V} = 6\cdot10^{-5}\ T^2 + 6,6\cdot10^{-3}\ T + 0,5536\tag{2}$$

La dernière étape pour déterminer la résistance thermique  $R_{BD}$ , a été l'assemblage du bloc chauffant, avec le film isolant électrique et le MOSFET. Le composant a été mis dans les mêmes conditions de travail où il avait été caractérisé, donc  $(V_{GS}=6\ V,\ V_{DS}=8\ V)$ , ce qui permet de déterminer la température de jonction en fonction du courant consommé  $I_{SAT}$  une fois l'équilibre thermique est atteint. Le courant  $I_{SAT}$  mesuré vaut  $I_{SAT}=2,11\ A$ , ce qui correspond à une température de jonction  $T_{J}=117\ ^{\circ}C$ . Étant donné que les pertes sont calculées en fonction du courant  $I_{SAT}$  et de la tension  $V_{DS}$ , que la température du bloc chauffante reste fixé à 80 °C, et que la résistance  $R_{JC}$  est connue, on peut déterminer la résistance  $R_{BD}$  comme suive (3) :

$$R_{BD} = \frac{T_J - T_D}{V_{DS} \cdot I_{SAT}} - R_{JC} = \frac{117 - 80}{16,88} - 0.65 = 1,55^{\circ} C / W \quad (3)$$

Suite à la détermination de cette résistance thermique, on peut calculer la température  $T_D$  à laquelle il faut régler le bloc chauffant(4), pour que la température de jonction soit égale à 150 °C.

$$T_D = T_I - P(R_{IR} + R_{RD}) (4)$$

Les pertes en commutation sur le DUT peuvent être négligées dans le cas où le canal du MOSFET reste tout le temps à l'état bloqué, car elles sont peu importantes sur une diode. La chute de tension directe de la diode à 150 °C avec une tension

de grille  $V_{GS}$ = -8 V a été mesurée à  $V_F$ =3,1 V pour  $I_{BD}$ =10 A. Étant donné que l'ondulation du courant (représenté ici par  $I_{SW}$ ) est faible à cause de la forte inductance utilisée, on peut considérer le courant circulant dans la diode comme une forme d'onde carrée. Donc, on calcule les pertes (5) ainsi que la température du bloc chauffant  $T_D$  (6) qu'il faudra régler à  $102~^{\circ}C$ .

$$P = V_F \cdot I_{RMS} = 3.1 V \cdot \frac{10 A}{\sqrt{2}} = 22 W$$

(5)

$$T_D = 150 - 22 \cdot (0.65 + 1.55) = 102 \,^{\circ} C$$

(6)

À cause des incertitudes sur l'impédance thermique du film isolant en fonction de la température et la pression appliquée, on estime une incertitude sur la température T<sub>J</sub> d'environ 10 °C.

#### 3.2. Test HTRB.

Dans la littérature on trouve [12] des études basées sous des tests standards JEDEC qui montrent une dérive de la tension de seuil, même sous conditions de fonctionnement statiques.

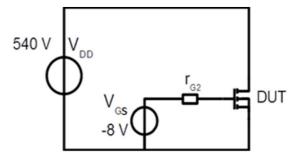

Un test HTRB classique (voir Fig.3) est réalisé sur une dizaine de composants afin de vérifier ce comportement sur les MOSFET sous test. Les conditions du test seront les mêmes que pour le banc de test CMB, donc une tension  $V_{\rm DD}$ =540 V et une tension de grille  $V_{\rm GS}$ =-8V, pour une durée du test de 400 heures.

Après une caractérisation initiale, les composants sont placés dans un four à 150 °C. Ils sont caractérisés à nouveau par intervalles de 100 heures, ainsi qu'au bout des dix premières heures du test avec un traceur de caractéristiques B1505. La caractérisation est faite à température ambiante.

Les résultats obtenus sont comparés avec les résultats montrés dans la littérature pour des tests similaires. Ainsi qu'avec la dégradation de la tension de seuil qu'on observera sur le banc de test CMB, donc sur les DUT sous conditions de fonctionnement dynamique.

#### 3.3. Test CMB – Canal toujours à l'état bloqué

Ce test est réalisé sur le banc de test CMB. L'objet l'étude est une éventuelle dégradation de la jonction P-N. À cette fin, la tension de grille du DUT est réglée à une tension constante  $V_{\rm GS}\!\!=\!\!-8$  V. Puis, le DUT restera continument à l'état bloqué, permettant la circulation du courant par la diode intrinsèque. Cependant, il faut remarquer que si la datasheet [26] autorise une tension de grille jusqu'à  $V_{\rm GS}\!\!=\!\!-10$  V, la dernière version incorpore une recommandation d'utilisation à  $V_{\rm GS}\!\!=\!\!-5$  V pour des applications où la diode intrinsèque est sollicitée.

Une caractérisation complète à température ambiante des composants testés est réalisée chaque 20 heures, ainsi qu'au bout des 10 premières heures de fonctionnement. La durée de l'essai est de 100 heures. Suite à une dérive observée sur la tension de seuil, le test est prolongé à 400 heures pour deux composants afin de vérifier l'évolution de cette dérive.

Fig.3 Schéma de principe d'un test HTRB.

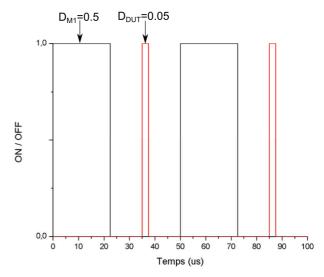

#### 3.4. Test CMB – Canal parfois à l'état passant

Un deuxième test est proposé pour étudier l'impact du rapport cyclique sur le DUT, car l'utilisation d'un MOSFET en permanence à l'état bloqué, et qui ne conduirait que par la diode intrinsèque, n'est pas réaliste. On veut vérifier si ce paramètre a une incidence sur la dégradation du MOSFET, notamment sur la dérive de la tension seuil. La tension de commande utilisée est  $V_{GS}$ =+20 V/-8 V.

Afin de soumettre la diode interne au même stress que dans le cas précédent, le rapport cyclique du composant M1 (voir Fig.2) est aussi changé. Le Tableau 2 montre les différents rapports cycliques (D) des interrupteurs pour chaque test, ainsi que le pourcentage de temps où la diode et le canal du DUT sont sollicités. Le seul cas où il n'est pas possible de garantir un temps de conduction de 50% de la période par la diode interne apparait pour D=0.85.

Les résultats obtenus sur ce test devront nous permettre dissocier les causes de la dérive de la tension seuil sur les expériences réalisées.

#### 4. RÉSULTATS EXPÉRIMENTAUX

Par la suite, on montre les résultats obtenus sur les expériences décrites ci-dessus.

#### 4.1. Test HTRB.

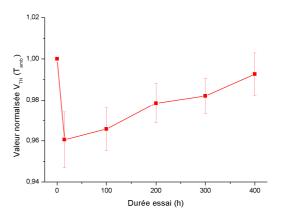

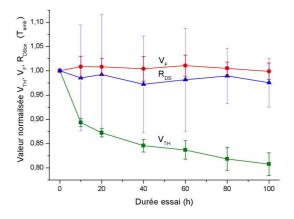

Le test HTRB, voir Fig.3, a été réalisé sur une dizaine de composants à 150°C. Suite aux résultats obtenus, la moyenne de la valeur normalisée de la tension de seuil a été calculée. Elle est représentée sur la Fig.4. Il est observé une chute de V<sub>TH</sub>, suite aux 10 premières heures de test, puis une récupération lente de la tension de seuil vers sa valeur initiale. Néanmoins, la chute de V<sub>TH</sub> est faible, toujours inférieure à 5%. Ces résultats sont plutôt rassurants, car dans la littérature on retrouve de tests HTRB ainsi que HTGB [12, 16], avec variations de la tension de seuil beaucoup plus importantes, peut-être sur une génération technologique plus ancienne. Concrètement, dans [12] on trouve des chutes de V<sub>TH</sub> jusqu'à 20% de la valeur initiale sur un test HTGB à V<sub>GS</sub>=-5 V. On y retrouve également des tests à V<sub>GS</sub>=-10 V où la tension de seuil chute dramatiquement, et qui sont en concordance avec les résultats montrés dans [16]. Il faut cependant remarquer que dans ces expériences les électrodes de drain et source sont en court-circuit (V<sub>DS</sub>=0V), donc nous ne sommes pas dans les mêmes conditions de test.

#### 4.2. Test CMB - Canal toujours à l'état bloqué

Le test CMB a été effectué sur une dizaine de composants. Malheureusement, un composant a subi une défaillance au bout des 10 premières heures de fonctionnement, avec une chute de la tension de seuil jusqu'à 0,47 V. L'étude n'a pas été poursuivie sur cet échantillon et donc la population du groupe d'étude est de neuf échantillons.

La Fig.5 montre l'évolution des paramètres  $V_{TH}$ ,  $R_{DS}$  et  $V_F$ . La courbe représentée est la moyenne normalisée de chaque paramètre. Il y a une dégradation de la tension de seuil, qui chute d'environ 20 %. Néanmoins, on observe que la vitesse d'évolution du  $V_{TH}$  des composants testés se réduit au cours de l'essai avec une dégradation plus lente. Il faudra poursuivre les tests afin de pouvoir déterminer si la tension de seuil tend à se stabiliser.

Il est observé (voir Fig.5) que la chute de tension de la diode  $V_F$  reste plutôt constante, ce qui indique une faible dégradation de la jonction P-N, qui ne mettrait pas en risque le fonctionnement du composant. Donc, sur les composants testés n'a pas été observée une dégradation de la jonction P-N telle

qu'on la retrouve dans la littérature [18, 16]. La résistance à l'état passante reste aussi assez stable, même si les mesures présentent des distorsions expérimentales.

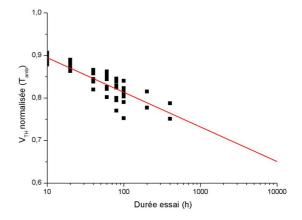

La Fig.6 montre la dégradation du  $V_{TH}$  extrapolée jusqu'à 10.000 h. Le lissage est obtenu par la méthode des moindres carrés. Suit à cette extrapolation, on estime la chute de la tension de seuil à environ 35% à 10.000.

Fig.4 Résultats des tests HTRB sur dix composants. Caractérisation à température ambiante,  $I_{DS}{=}100~\mu A,~V_{DS}{=}1~V.$  Les valeurs indiquées sont les moyennes de la tension de seuil normalisée.

Fig.5 Évolutions normalisées de  $V_{TH}$ ,  $V_F$ ,  $R_{DS}$  obtenues sur le banc de test CMB. Caractérisation à température ambiante.  $V_F$  ( $V_{GS}$ =-8 V, $I_{SD}$ =10 A),  $R_{DS}$  ( $V_{GS}$ =20 V,  $I_{DS}$ =10 A),  $V_{TH}$  ( $I_{DS}$ =100  $\mu$ A,  $V_{DS}$ =1 V). Les valeurs indiquées sont les moyennes normalisées.

Fig.6 Évolution et extrapolation de  $V_{TH}$  normalisée obtenue sur le banc de test CMB. Caractérisation à température ambiante,  $I_{DS}$ =100  $\mu$ A,  $V_{DS}$ =1 V.

#### 4.3. Test CMB – Canal parfois à l'état passant

Afin d'approfondir l'étude de la dérive de la tension de seuil  $V_{TH}$  observée sur le test présenté dans la section précédente, nous avons procédé à un test dans des conditions plus réalistes. Il s'agit d'un test où le DUT conduit un temps par la diode interne, puis un temps par le canal (voir Tableau 2 et Fig.7).

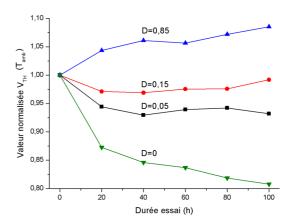

La Fig.8 montre l'influence de la conduction de la diode interne par l'intermédiaire du rapport cyclique D sur la dégradation de la tension seuil. Les cas où le rapport cyclique est D=0, D=0.05 et D=0.15 peuvent être comparés car la diode continue à conduire pendant 50% de la période. Il est observé que pour des faibles rapports cycliques (5%-15%), la tension de seuil montre une faible dégradation, inférieure à 8 %, et une certaine stabilisation au cours des essais.

Pour les forts rapports cycliques (D=0.85), il y a une augmentation de la tension de seuil d'environ 8 %. Il faut vérifier l'évolution de cette dérive et son influence qui pourrait entrainer une augmentation de la résistance interne du composant, donc des pertes par conduction. Sur le DUT, il a été mesuré une augmentation de  $R_{\rm DS}$  du 2.6%.

#### 5. CONCLUSIONS

Si le MOSFET en silicium est aujourd'hui assez robuste avec une durée de vie supérieure à plusieurs dizaines de milliers d'heures, ce travail, ainsi que la littérature montrent que les MOSFET SiC actuels continuent de présenter des problèmes de fiabilité liés à l'oxyde de grille, quel que soit le fabricant. La jonction P-N de la diode interne ne montre pas de dégradation importante lors qu'elle est sollicitée en conduction. Toutefois les différentes études menées sur ces composants aboutissent à des résultats parfois différents, notamment en fonction des conditions d'essai.

La dérive de la tension de seuil est, a priori due, à l'injection et au piégeage de porteur de charges à l'interface SiO2/SiC voire dans l'oxyde. Cette injection dépend donc de la polarité de la tension appliquée à la grille et à la durée d'application et donc du rapport cyclique. Il est donc normal de constater une dépendance des tensions appliquées et du rapport cyclique.

Les expériences réalisées montrent que les tests standardisés pour les MOSFET et IGBT en silicium ne sont pas bien adaptés aux composants SiC. La dégradation de l'oxyde de grille en mode hacheur est plus sévère qu'en statique (HTRB), ce qui suggère que des phénomènes d'injection de porteurs existent lors des phases de commutation que l'interrupteur M1 induit sur le DUT. Nous devrons donc toutefois approfondir l'étude notamment pour étudier le rôle éventuel des commutations internes ou induites.

Les tests avec le canal du MOSFET toujours à l'état bloqué, montent une importante dégradation de la tension de seuil, si bien qu'elle semble suivre une dérive logarithmique, et donc, la dérive est beaucoup plus faible après les premières heures de fonctionnement. On estime la chute de la tension de seuil à environ 35% et 43% à 10.000 et 100.000 heures de fonctionnement respectivement. L'utilisation de la diode interne est donc possible notamment pour des applications « diode-less », dans l'attente d'une étude plus approfondie.

À propos du driver, pour éviter des problèmes de remise en conduction avec une tension de seuil devenue trop faible, il est recommandé d'utiliser d'une tension négative de blocage. Dans le cas où les tests montreraient un prolongement de la dégradation de la tension de seuil, il faudrait mettre en œuvre un suivi de la tension de seuil à fin d'empêcher des défaillances du système.

Tableau 2. Résumé des temps de conduction.

| D <sub>DUT</sub> (%) | Temps<br>conduction<br>D <sub>M1</sub> (%) | Temps conduction<br>diode intrinsèque<br>DUT (%) | Temps conduction canal DUT (%) |

|----------------------|--------------------------------------------|--------------------------------------------------|--------------------------------|

| 0 %                  | 50 %                                       | 50 %                                             | 0 %                            |

| 5 %                  | 45 %                                       | 50 %                                             | 5 %                            |

| 15 %                 | 35 %                                       | 50 %                                             | 15 %                           |

| 85 %                 | 13.4 %                                     | 1.6 %                                            | 85 %                           |

Fig.7 État logique des interrupteurs M1 et DUT pour D<sub>DUT</sub>=5%.

Fig.8 Évolution de  $V_{TH}$  normalisée sur le banc de test CMB à différents rapports cycliques  $D_{DUT}$  (voir Tableau 2). Caractérisation à température ambiante,  $I_{DS}{=}100~\mu A,~V_{DS}{=}1~V.$

#### 6. References

- E. G. Acheson, «Carborundum: Its history, manufacture and uses,» Journal of the Franklin Institute, pp. 279-289, 1893.

- [2] R. N. Hall, «Silicon carbide semiconductor devices and method of preparation thereof». Brevet US2918396, 1959.

- [3] J. Palmour, H. Kong et R. Davis, «Mosfet in Silicon Carbide». Brevet WO1989004056, 1988.

- [4] P. Friedrichs, «SiC Power Devices Lessons Learned and Prospects After 10 Years of commercial Availability,» chez CS MANTECH Conference, Palm Springs, California, 2011.

- [5] P. Neudeck, «Study of bulk and elementary screw dislocation assisted reverse breakdown in low-voltage (<250 V) 4H-SiC p+-n junction diodes. I. DC properties,» IEEE Transactions on Electron Devices, vol. 46, no. 3, pp. 478-484, 2002.

- [6] T. Kimoto, "Performance limiting surface defects in SiC epitaxial p-n junction diodes," IEEE Transactions on Electron Devices, vol. 46, no.3, pp. 471-477, 1999.

- [7] H. Chen, B. Raghothamachar, W. Vetter, M. Dudley, Y. Wang et B. J. Skromme, «Effects of Different Defect Types on the Performance of Devices Fabricated on a 4H-SiC Homoepitaxial Layer,» MRS Proceddings, vol. 911, pp. 0911-B12-03, 2006.

- [8] V. V. Afanasev, M. Bassler, G. Pensl et M. Schulz, «Intrinsic SiC/SiO2 Interface States,» Phys. stat. sol., vol. 162, no. 1, pp. 321-337, 1997.

- [9] S. Potbhare, N. Goldsman, G. Pennington, A. Lelis et J. M. McGarrity, «A quasi-two-dimensional depth-dependent mobility model suitable for device simulation for Coulombic scattering due to interface trapped charges,» J. App. Phys., vol. 100, p. 044516, 2006.

- [10] S. Tanimoto et H. Ohashi, «Reliability issues of SiC power MOSFETs toward high junction temperature operation,» Phys. Status Solidi A, vol. 206, p. 2417–2430, 2009.

- [11] C. Chen, D. Labrousse, S. Lefebvre, M. Petit, C. Buttay et H. Morel, «Robustness in short-circuit Mode of SiC MOSFETs,» chez PCIM, 2015.

- [12] L. Yang et A. Castellazzi, «High temperature gate-bias and reverse-bias tests on SiC MOSFETs,» Microelectronics Reliability, vol. 53, pp. 1771-1773, 2013.

- [13] A. Fayyaz et A. Castellazzi, «High temperature pulsed-gate robustness testing of SiC power MOSFETs,» Microelectronics Reliability, 2015.

- [14] R. Singh, «Reliability and performance limitations in SiC power devices,» Microelectronics reliability, vol. 46, pp. 713-730, 2006.

- [15] S. Ryu, H. Fatima, S.Haney, Q. Zhang, R.Stahlbush et A. Agarwal, «Effect of recombination-induced stacking faults on majority carrier conduction and reverse leakage current in 10 kV SiC DMOSFETs,» Mater. Sci. Forum, Vol. 600-603, pp. 1127-1130, 2009.

- [16] O. Kusumoto, A. Ohoka, N. Horikawa, K. Tanaka, M. Niwayama, M. Uchida, Y. Kanzawa, K. Sawada et T. Ueda, «Reliability of Diode-Integrated SiC Power MOSFET(DioMOS),» Microelectronics Reliability, vol. 58, pp. 158-163, 2016.

- [17] R. Pittini, Z. Zhang et M. Andersen, «Switching performance evaluation of commercial SiC power devices (SiC JFET and SiC MOSFET) in relation to the gate driver complexity,» ECCE Asia, pp. 233-239, 2013.

- [18] T. Ueda, «Reliability issues in Gan and SiC power devices,» chez IEEE International Reliability Physics Symposium, Waikoloa, HI, 2014.

- [19] A. Lelis, D. Habersat and R. Green, "High-Temperature Reliability of SiC Power MOSFETs," Materials Science Forum, Vols. 679-680, pp. 599-602, 2011.

- [20] B. Schlund, C. Messick, J. Suehle et P. Chaparala, «A new physics-based model for time-dependent-dielectric-breakdown,» Reliability Physics Symposium, 1996. 34th Annual Proceedings., IEEE International, pp. 84-92, 1996.

- [21] E. Takeda, N. Suzuki et T. Hagiwara, «Device performance degradation to hot-carrier injection at energies below the Si-SiO2energy barrier,» Electron Devices Meeting, 1983 International, vol. 29, pp. 396-399, 1983

- [22] JEDEC, JESD22-A108D, Temperature, Bias and Operating Life, 2010.

- [23] D. A. Gajewski, S. H. Ryu, M. Das, B. Hull, J. Young and J. W. Palmour, "Reliability Performance of 1200 V and 1700 V 4H-SiC DMOSFETs for Next Generation Power Conversion Applications," Materials Science Forum, Vols. 778-780, pp. 967-970, 2014.

- [24] M. K. Das, J. Sumakeris, B. Hull et J. Richmond, «Evolution of Drift-Free, High Power 4H-SiC PiN Diodes,» Materials Science Forum, Vols. 527-529, pp. 1329-1334, 2006.

- [25] J. Sumakeris, P. Bergman, M. Das, C. Hallin, B. Hull, E. Jazén, H. Lendenmann, M. O'Louglin, M.J.Paisley, S. Ha, M. Skowronski, J. Palmour et C. C. Jr., «Techniques for Minimizing the Basal Plane Dislocation Density in SiC Epilayers to Reduce Vf Drift in SiC Bipolar Power Devices,» Materials Science Forum, Vols. 527-529, pp. 141-146, 2006.

- [26] I. Cree, «C2M0080120D Silicon Carbide Power Mosfet Datasheet,» Durham, 2014.