## Compilation efficace de spécifications de contrôle embarqué avec prise en compte de propriétés fonctionnelles et non-fonctionnelles complexes

Thomas Carle

#### ▶ To cite this version:

Thomas Carle. Compilation efficace de spécifications de contrôle embarqué avec prise en compte de propriétés fonctionnelles et non-fonctionnelles complexes. Base de données [cs.DB]. Université Pierre et Marie Curie - Paris VI, 2014. Français. NNT: 2014PA066392. tel-01088786

#### HAL Id: tel-01088786 https://inria.hal.science/tel-01088786

Submitted on 28 Nov 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

#### Spécialité Informatique

(École Doctorale Informatique, Télécommunication et Électronique)

#### Présentée par THOMAS CARLE

Pour obtenir le grade de DOCTEUR DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

## COMPILATION EFFICACE DE SPÉCIFICATIONS DE CONTRÔLE EMBARQUÉ AVEC PRISE EN COMPTE DE PROPRIÉTÉS FONCTIONNELLES ET NON-FONCTIONNELLES COMPLEXES

Soutenue le 31 Octobre 2014, devant le jury composé de

| Prof. | ISABELLE PUAUT         | IRISA           | Rapportrice        |

|-------|------------------------|-----------------|--------------------|

| Prof. | François Irigoin       | Mines ParisTech | Rapporteur         |

| Prof. | ALIX MUNIER            | UPMC            | Examinatrice       |

| Dr.   | DAVID LESENS           | Airbus DS       | Examinateur        |

| Prof. | Laurent George         | ESIEE           | Examinateur        |

| Dr.   | DUMITRU POTOP-BUTUCARU | INRIA           | Directeur de thèse |

## PH.D. THESIS OF THE UNIVERSITY PIERRE AND MARIE CURIE

Department : COMPUTER SCIENCE AND MICRO-ELECTRONICS

Presented by: THOMAS CARLE

Thesis submitted to obtain the degree of DOCTOR OF THE UNIVERSITY PIERRE AND MARIE CURIE

# EFFICIENT COMPILATION OF EMBEDDED CONTROL SPECIFICATIONS WITH COMPLEX FUNCTIONAL AND NON-FUNCTIONAL PROPERTIES

Defence on October 31st, 2014, Committee:

| Prof. | ISABELLE PUAUT         | IRISA           | Reviewer |

|-------|------------------------|-----------------|----------|

| Prof. | François Irigoin       | Mines ParisTech | Reviewer |

| Prof. | ALIX MUNIER            | UPMC            | Examiner |

| Dr.   | DAVID LESENS           | Airbus DS       | Examiner |

| Prof. | Laurent George         | ESIEE           | Examiner |

| Dr.   | DUMITRU POTOP-BUTUCARU | INRIA           | Advisor  |

#### Remerciements

Je tiens à remercier ici Dumitru Potop-Butucaru, mon directeur de thèse, pour la confiance qu'il m'a accordée, pour tous les conseils qu'il m'a prodigués, pour sa disponibilité et sa patience tout au long de ma thèse, pour son ouverture d'esprit et pour son implication sans faille à mes côtés tant durant cette thèse que pour la préparation de mon avenir.

J'aimerais également remercier Isabelle Puaut et François Irigoin, qui ont accepté d'être les rapporteurs de cette thèse, pour leurs remarques constructives qui m'ont permis de prendre du recul sur mon travail et de l'améliorer. Je remercie de même Alix Munier, David Lesens et Laurent George de m'avoir fait l'honneur d'accepter de participer à mon jury.

Je voudrais remercier les membres passés et présents de mon équipe pour leur bienveillance et leur sympathie, ainsi que pour leurs conseils et leur soutien dans les moments difficiles, notamment de la rédaction. Mes pensées vont notamment vers Manel Djemal, Raul Gorcitz, Abderraouf Benyahia, Walid Talaboulma, Falou N'doye, Daniel de Rauglaudre, Cécile Stentzel, Yves Sorel, Liliana Cucu-Grosjean, Adriana Gogonel et Codé Lo.

Enfin, je remercie ma famille et mes amis, et plus particulièrement mes parents pour m'avoir soutenu tout au long de mes (longues) études.

<sup>&</sup>quot;Un jour viendra où ces avaleurs de feu que nous sommes se mettront à le cracher, et notre plus belle création sera l'œuvre des incendies que nous aurons ainsi allumés."

## **Contents**

| Re      | Remerciements     |                                                                                              |          |  |  |

|---------|-------------------|----------------------------------------------------------------------------------------------|----------|--|--|

| Re      | ésumé             |                                                                                              | 6        |  |  |

| Al      | ostrac            |                                                                                              | 17       |  |  |

| 1       | 1.1<br>1.2<br>1.3 | 2 Compilation vs. Real-time scheduling                                                       |          |  |  |

| I<br>th |                   | ine scheduling: fundamental notions and contributions cification models for embedded systems | on<br>28 |  |  |

| 2       | Intr              | duction to synchronous formalisms                                                            | 29       |  |  |

|         | 2.1               | The synchronous model of computation                                                         | . 29     |  |  |

|         |                   | 2.1.1 Abstraction issues                                                                     | . 30     |  |  |

|         |                   | 2.1.2 Clocks and Single-clock synchronous languages                                          | . 31     |  |  |

|         |                   | 2.1.3 Polychronous languages                                                                 | . 32     |  |  |

|         |                   | 2.1.4 Languages with affine clocks                                                           | . 32     |  |  |

|         |                   | 2.1.5 From logical time to real time                                                         | . 33     |  |  |

| 3       | Fun               | tional specification                                                                         | 35       |  |  |

|         | 3.1               | Introduction                                                                                 | . 35     |  |  |

|         | 3.2               | The Clocked Graph synchronous language                                                       | . 37     |  |  |

|         |                   | 3.2.1 Host language and global definitions                                                   |          |  |  |

|         |                   | 3.2.2 Dataflow definition                                                                    |          |  |  |

|         |                   | 3.2.3 Well-formed properties                                                                 |          |  |  |

|         |                   | 3.2.4 Example                                                                                |          |  |  |

|         | 3.3               | Translation from higher-level specifications                                                 |          |  |  |

|         |                   | 3.3.1 Functional specifications in SynDEx                                                    |          |  |  |

|         | 2 1               | 3.3.2 Translation technique                                                                  |          |  |  |

|         | 3.4               | Abstraction as single-period task systems                                                    |          |  |  |

|         | 3.5               | Modeling multi-period task systems                                                           |          |  |  |

|         | 3.6               | Conclusion                                                                                   | . 68     |  |  |

| 4  | Mod   | leling resources and resource allocation                               | 69  |

|----|-------|------------------------------------------------------------------------|-----|

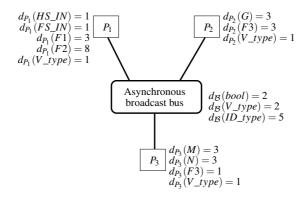

|    | 4.1   | Resource description formalism                                         | 72  |

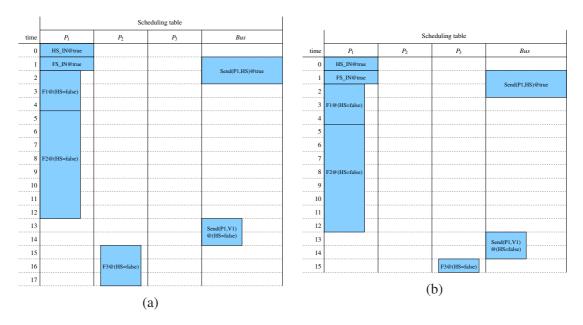

|    | 4.2   | Scheduling tables                                                      | 74  |

|    |       | 4.2.1 Table-based off-line scheduling (the principle)                  | 76  |

|    |       | 4.2.2 Scheduling tables in LoPhT                                       | 82  |

|    | 4.3   | Conclusion                                                             | 88  |

|    |       |                                                                        |     |

| II | So    | ftware pipelining of scheduling tables                                 | 90  |

| 5  | Evto  | ensions of the basic formalism                                         | 91  |

| J  | 5.1   | Memory representation for pipelining                                   | 92  |

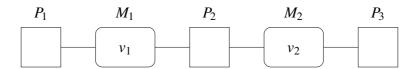

|    | 5.1   | 5.1.1 Architecture model                                               | 92  |

|    |       | 5.1.2 Implementation model                                             | 93  |

|    |       | 5.1.3 A simple example                                                 | 94  |

|    |       | 5.1.4 Well-formed properties                                           | 94  |

|    | 5.2   | Conclusion                                                             | 95  |

|    | 3.2   | Conclusion                                                             | 93  |

| 6  | Thre  | oughput optimization by software pipelining of conditional reservation | Į   |

|    | table | es                                                                     | 96  |

|    | 6.1   | Related work and originality                                           | 100 |

|    |       | 6.1.1 Decomposed software pipelining                                   | 100 |

|    |       | 6.1.2 Originality                                                      | 102 |

|    |       | 6.1.3 Other aspects                                                    | 104 |

|    | 6.2   | Pipelining technique overview                                          | 104 |

|    |       | 6.2.1 Representing a pipelined scheduling table                        | 104 |

|    | 6.3   | Optimization algorithms                                                | 111 |

|    |       | 6.3.1 Dependency graph and maximal throughput                          |     |

|    |       | 6.3.2 Dependency analysis and main routine                             | 113 |

|    |       | 6.3.3 Complexity considerations                                        | 118 |

|    | 6.4   | Code generation                                                        |     |

|    |       | 6.4.1 Memory management issues                                         | 118 |

|    | 6.5   | Experimental results                                                   |     |

|    | 6.6   | Conclusion                                                             | 125 |

|    |       |                                                                        |     |

| II | I R   | eal-time scheduling and code generation under complex non-             |     |

| fu | nctio | onal constraints                                                       | 127 |

| 7  | Exte  | ensions of the Clocked Graph formalism                                 | 128 |

| •  | 7.1   | <u>-</u>                                                               | 131 |

|    | 7.2   |                                                                        | 134 |

|    |       | 7.2.1 Time-triggered systems                                           |     |

|    |       |                                                                        | 136 |

|    |       |                                                                        | 137 |

|    | 7.3   | Modeling of the aerospace case study                                   |     |

|    |       |                                                                        | 140 |

|    |         | 7.3.2 Representing execution modes                           | 41        |

|----|---------|--------------------------------------------------------------|-----------|

|    | 7.4     | Non-functional properties                                    | 42        |

|    |         | 7.4.1 Period, release dates, and deadlines                   |           |

|    |         | 7.4.2 Worst-case durations, allocations, preemptability      | 45        |

|    |         | 7.4.3 Partitioning                                           |           |

|    |         | 7.4.4 Syntax extensions                                      |           |

|    | 7.5     | Conclusion                                                   |           |

| 8  | Real    | Time scheduling under complex non-functional requirements 15 | 52        |

|    | 8.1     | Removal of delayed dependencies                              | 53        |

|    | 8.2     | Offline real-time scheduling                                 |           |

|    |         | 8.2.1 Basic principles                                       |           |

|    |         | 8.2.2 Scheduling algorithm                                   |           |

|    |         | 8.2.3 Complexity and optimality considerations               |           |

|    |         | 8.2.4 Scheduling results                                     |           |

|    | 8.3     | Post-scheduling slot minimization                            |           |

|    | 8.4     | Partitioned time-triggered code generation                   |           |

|    |         | 8.4.1 Automatic synthesis of communication channels          |           |

|    |         | 8.4.2 Process number minimization                            |           |

|    | 8.5     | Conclusion                                                   |           |

| 9  | Con     | lusion and perspectives 17                                   | 71        |

|    | 9.1     | Conclusion                                                   | 71        |

|    | 9.2     | Perspectives                                                 |           |

| A  | Mod     | eling NoC-based many-cores                                   | 76        |

| Li | st of l | ublications 17                                               | <b>78</b> |

| Bi | bliogi  | aphy 17                                                      | <b>79</b> |

#### Résumé

#### Conception de systèmes embarqués

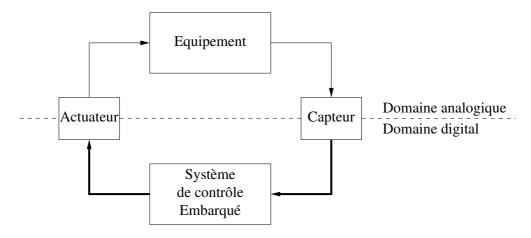

Les systèmes embarqués sont des systèmes informatiques ayant une fonction dédiée, au sein d'un système physique ou informatique plus large. Dans cette thèse, nous nous intéressons en particulier aux systèmes de contrôle embarqué [Lee and Seshia, 2011], dont le rôle est de réguler l'évolution de processus (physiques) afin d'assurer la correction de leur fonctionnement. Ici, les termes contrôle et régulation sont compris dans le sens de la théorie du contrôle [Doyle et al., 1990], c'est à dire qu'un système de contrôle embarqué est vu comme le moyen d'effectuer le *contrôle automatique* d'un équipement comme un avion, un train, un réacteur nucléaire, un téléphone mobile, etc. Comme on le voit dans la figure 1, un système de contrôle embarqué intéragit avec l'équipement contrôlé par le biais de *capteurs* et d'actuateurs. Les capteurs mesurent des caractéristiques (analogiques) spécifiques de l'équipement, et présentent l'information correspondante sous une forme discrétisée, permettant un traitement digital par le contrôleur embarqué. Les valeurs de retour discrètes du contrôleur sont utilisées par les actuateurs pour exercer un contrôle (analogique) sur l'équipement.

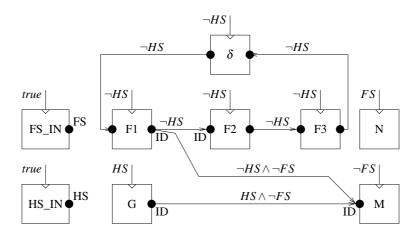

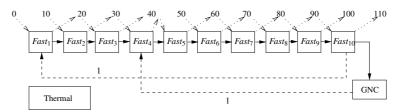

Figure 1: Interaction entre un équipement et un système de contrôle embarqué

Un exemple de ces interactions est donné par les contrôleurs embarqués de guidage, navigation et contrôle (GNC) des avions. Ceux-cis utilisent différents capteurs (de pression, de température, GPS, accéléromètres, gyroscopes, *etc.*) pour déterminer l'emplacement, la vitesse, le roulis, le tangage et le lacet de l'appareil. Ces valeurs sont utilisées de manière cyclique par le contrôleur GNC pour manipuler la position des ailerons et la puissance des réacteurs (par le biais d'actuateurs), afin de maintenir la trajectoire désirée. La conception de systèmes de contrôle embarqué est inter-disciplinaire. A haut niveau, elle est dirigée par des ingénieurs contrôle commande et par des ingénieurs système. Les

ingénieurs contrôle commande fournissent une spécification du comportement attendu du contrôleur, incluant ses fonctionnalités et ses besoins en termes temporels. Définir les fonctionnalités d'un système consiste à spécifier les opérations qui doivent s'exécuter ainsi que leur ordre d'exécution, pour calculer les commandes des actuateurs à partir des valeurs produites par les capteurs<sup>1</sup>. Cependant, la spécification fonctionnelle seule n'est pas suffisante pour traduire le comportement d'un système de contrôle. Pour assurer un contrôle effectif, les changements dans les processus physiques de l'équipement considéré doivent être suivis *en temps voulu* par des changements dans les actuateurs. Par exemple, le contrôleur embarqué GNC évoqué plus haut doit réagir rapidement aux coups de vent latéraux afin de maintenir la stabilité de l'avion, particulièrement lors des phases d'atterrissage. C'est pour cette raison que la partie correspondant au contrôle d'attitude du contrôleur GNC est exécutée une fois toutes les 50ms [Kent and Williams, 2002].

La spécification de ces contraintes temporelles s'effectue sous la forme de *contraintes* temps-réel telles que des périodes, des latences, des dates de déclenchement et des échéances qui sont attachées aux divers éléments de la spécification fonctionnelle. Les systèmes de contrôle embarqué appartiennent donc à la catégorie des systèmes temps-réel [Butazzo, 2002], qui forment eux-même une sous-classe des systèmes réactifs [Harel, 1987].

Alors que les ingénieurs contrôle commande spécifient le comportement des contrôleurs embarqués, les ingénieurs système étudient le problème de leur implantation, et fournissent des outils permettant de les gérer durant toute leur durée de vie. Cette durée de vie s'élève à plus de 20 ans pour un avion commercial, plus de 30 ans pour un réacteur nucléaire, et plus de 150000km en moyenne pour une voiture. A haut niveau, l'ingénierie des systèmes considère des propriétés macroscopiques telles que le coût (de développement, de maintenance, et parfois de mise hors service), la fiabilité (pour des raisons de cout et de sécurité), le risque, etc. Ces objectifs macroscopiques peuvent être traduits en termes de besoins non-fonctionnels, et l'ingénierie des systèmes fournit des méthodes pour raffiner de tels besoins de haut niveau et définir des besoins de plus bas niveau tels que ceux que nous considérons dans cette thèse. Par exemple, le chapitre 7 considère les besoins d'ingénierie système suivants : la plateforme d'exécution est fixée<sup>2</sup>, chaque opération de la spécification fonctionnelle s'est vue assignée un niveau de criticité, certaines de ces opérations peuvent être préemptées (les autres sont dites non préemptables), et une partie de la distribution des opérations de la spécification fonctionnelle sur les ressources de la plateforme est également déjà fixée. D'autres propriétés non-fonctionnelles qu'il est possible de considérer à ce niveau sont, par exemple, la tolérance aux pannes, la consommation d'énergie et l'évolutivité du système. C'est le niveau auquel mon travail se place : dans cette thèse je considère que les phases préliminaires d'ingénierie ont pro-

<sup>&</sup>lt;sup>1</sup>L'état interne du système peut aussi être utilisé.

<sup>&</sup>lt;sup>2</sup>Cela peut également imposer des contraintes temps-réel supplémentaires, en plus des celles provenant de la spécification du contrôle.

duit une spécification fonctionnelle, ont fixé l'architecture d'exécution cible (qui peut être une architecture multiprocesseur/distribuée), et ont généré un ensemble de besoins nonfonctionnels qui inclut notamment des contraintes temps-réel. A partir de ces données, mon objectif est de construire automatiquement un système de contrôle embarqué correct. La correction implique ici deux aspects : la correction fonctionnelle et le respect des besoins non-fonctionnels. La correction fonctionnelle se traduit par le fait que le système se comporte tel que la spécification fonctionnelle le prescrit. Assurer la correction fonctionnelle d'un tel système implique plusieurs disciplines telles que la compilation (pour assurer que chaque opération de la spécification est correctement implantée par du code séquentiel), le calcul parallèle/distribué (pour la construction d'implantations multiprocesseurs correctes), etc. Un domaine revêtant une importance particulière est celui de la conception et de l'implantation de langages synchrones qui regroupent toutes les disciplines nécessaires pour assurer la correction fonctionnelle. Cela est dû au fait que les langages et formalismes synchrones, qui seront décrits dans la thèse, ont été conçus spécifiquement pour permettre la spécification de systèmes de contrôle embarqué. Cela explique leur omniprésence dans la conception des systèmes embarqués et leur utilisation dans cette thèse.

Assurer le respect de besoins non-fonctionnels tels que ceux listés plus haut (temps-réel, criticité, préemptabilité, consommation d'énergie, *etc.*) est principalement étudié dans le domaine de *l'ordonnancement temps-réel*, qui lui même tire avantage de résultats venant de la conception de matériel et de systèmes d'exploitation, du calcul parallèle/distribué, de la tolérance aux pannes, *etc.*

Plaidoyer pour une intégration renforcée. La conception d'un système embarqué complexe rassemble en général des experts venant des domaines cités précédemment. Cependant, dans les travaux scientifiques et dans la pratique industrielle actuels, ces domaines restent largement séparés. Mon opinion est qu'une telle ségrégation a pour résultat d'augmenter les coûts de conception et de dégrader l'efficacité de l'implantation. Cela est dû à deux principales causes :

• Les interfaces entre les différents domaines, souvent matérialisées par des transformations de modèles, ont tendance à abstraire des détails significatifs présents dans les modèles de départ, ce qui entraine une perte d'efficacité. Cette perte d'efficacité est souvent accompagnée de l'utilisation d'abstractions peu sûres, qui imposent que la validation du système passe par une phase de tests intensive, ce qui augmente les coûts de développement<sup>3</sup>,

<sup>&</sup>lt;sup>3</sup>Par exemple, les modèles de tâches utilisés dans le domaine de l'ordonnancement temps-réel font souvent l'abstraction de tout le contrôle conditionnel attaché aux tâches, ce qui ajoute du pessimisme à l'analyse. De plus, beaucoup de modèles de tâches utilisés dans le cadre d'ordonnancement multipro-

• Le manque de communication entre les communautés scientifiques et industrielles implique que des solutions développées dans un domaine ne seront pas appliquées dans un autre, même lorsque cela serait approprié.

Le travail réalisé durant cette thèse s'attaque à ces deux points pour des classes spécifiques d'architectures cibles. Afin de réduire la perte d'efficacité nous utilisons des modèles précis des applications (où le contrôle conditionnel est pris en compte), des architectures (où les coûts de communication et les mécanismes d'exécution précis sont considérés), et des besoins non-fonctionnels, qui sont adaptés à nos plateformes d'exécution cibles (des systèmes partitionnés dirigés par le temps). La modélisation précise de la plateforme d'exécution réduit également le recours à des abstractions non sûres. Néanmoins la contribution principale de ma thèse s'articule autour du second axe. Plus précisément, je vais montrer que par l'intégration de concepts provenant de l'ordonnancement tempsréel, de la compilation et de la programmation synchrone, nous sommes en mesure de produire automatiquement des implantations temps-réel dirigées par le temps à la fois correctes par construction (et qui ont donc besoin de moins de travail de validation) et plus efficaces que celles produites par les approches existantes jusqu'alors. Dans notre cas, cela revient à appliquer une approche de type compilation lors de la synthèse d'implantations temps-réel à partir de spécifications qui sont complexes à la fois dans leurs aspects fonctionnels et non-fonctionnels. Réciproquement, on peut également voir cela comme une extension de l'état de l'art de la compilation, afin de prendre en compte des besoins non-fonctionnels et de permettre une prise en compte précise des temps d'exécution au pire cas dans le processus de compilation.

#### Comparaison entre compilation et ordonnancement tempsréel

Une séparation existe de longue date entre les domaines de la construction de compilateurs et de l'ordonnancement temps-réel. Si ces deux domaines ont le même objectif - la construction d'implantations correctes - la séparation se justifie historiquement par des différences significatives entre les modèles et les méthodes utilisés. En effet, les travaux initiaux dans la communauté de la compilation se sont concentrés sur la génération de code machine séquentiel et ordonnancé statiquement. L'objectif des optimisations était d'améliorer la vitesse d'exécution du cas moyen, mais sans fournir de garantie formelle d'optimalité ou de performance. L'optimisation était basée sur l'exploitation

cesseur font l'hypothèse que les communications ne prennent pas de temps. Pour que cette abstraction reste sûre, les durées au pire cas des communications doivent être prises en compte en ajoutant des marges de sécurité dans les durées caractérisant les tâches. Cependant, dans la plupart des cas, ces marges ne sont pas calculées en utilisant une analyse formelle du matériel et des protocoles de communication.

d'informations détaillées concernant la microarchitecture. Etant donné la nature du problème à résoudre, un compilateur devait *toujours retourner un résultat* pour un programme syntactiquement correct.

Dans les premiers systèmes temps-réel multi-tâches, les compilateurs fournissaient les tâches séquentielles que le système d'exploitation executait. La conception et l'analyse au niveau système constituaient l'objet de travail de la communauté de l'ordonnancement temps-réel. Les travaux sur ce sujet, tel que l'article fondateur de Liu et Layland [Liu and Layland, 1973], tentaient de fournir des garanties d'ordonnançabilité formelles pour des tâches exécutées par un ordonnanceur dynamique/en ligne (et souvent preemptif). Au contraire de la compilation, où l'objectif est la synthèse complète d'un morceau de code, l'ordonnancement temps-réel ne synthétise pas ou peu de paramètres de l'implantation (par exemple, les priorités des tâches, ou l'allocation des tâches sur les processeurs dans un système distribué). L'analyse d'ordonnancement était basée sur des abstractions fortes des tâches et de la plateforme d'exécution, appelées modèles de tâches. Assurer qu'une telle abstraction forte est sûre est un sujet rarement couvert dans les articles d'ordonnancement temps-réel. Cela représentait un problème significatif lors de la mise en pratique industrielle, et particulièrement parce que l'implantation du système était elle même produite pour la plupart à la main (contrairement à une compilation complètement automatique, où tous les aspects de l'ordonnancement et de la génération de code seraient contrôlés par le compilateur). Enfin, l'analyse d'ordonnançabilité pouvait échouer. Les différences entre les modèles et les méthodes mentionnés plus haut sont d'une importance certaine, et peuvent expliquer la séparation initiale entre les communautés de recherche et d'ingénierie. Cependant, ces deux domaines ont significativement évolué depuis. Lors de la conception de techniques de compilation pour les architectures superscalaires et VLIW, la communauté de la compilation a introduit une prise en compte précise des durées d'exécution ainsi que l'utilisation de multiples resources indépendantes. Plus récemment, elle a considéré des modèles d'architecture moins précis et des modèles d'exécution plus dynamiques pour permettre la compilation vers des cibles GPU. D'un autre côté, les approches temps-réel basées sur l'ordonnancement statique/hors ligne, plutôt que sur l'ordonnancement dynamique/en ligne, ont gagné en importance lorsque des besoins industriels ont mené à la définition de standards tels que IMA/ARINC 653 (pour les systèmes avioniques), AUTOSAR (pour les systèmes automobiles), ou TTA, FlexRay, TTEthernet (pour les bus de communication). Qui plus est, les systèmes basés sur ces standards nécessitent d'être configurés en détail (ce qui peut nécessiter de synthétiser l'information de configuration), ce qui a pour conséquence la nécessité d'avoir recours à des approches de type compilation pour traiter tous les aspects de l'implantation, et pas seulement l'ordonnancement.

Dès lors, sans pour autant se confondre entièrement, les objets d'étude de ces deux

communautés se recouvrent aujourd'hui largement, ce qui justifie une mise en commun des efforts de recherche et d'ingénierie. De plus, dans ce processus de mutualisation, un troisième domaine peut jouer un rôle important : la conception et l'implantation de langages synchrones.

Comme il est écrit au chapitre 2, les premiers langages synchrones ont été introduits par la communauté du temps réel dans le but de permettre la spécification (formellement complète) de systèmes de contrôle embarqué complexes. Ces systèmes sont de taille importante, et nécessitent donc le recours à une modélisation hiérarchique, et incluent des structures de contrôle complexes, qui impliquent de la concurrence, du contrôle conditionnel, de la préemption, et des comportements à états qui ne peuvent pas être bien représentés par les modèles de tâches très abstraits. L'étude des langages et formalismes synchrones sont devenus un domaine de recherche indépendant qui a des applications dans la spécification, l'analyse formelle, et l'implantation à la fois des systèmes embarqués et de la conception matérielle [Benveniste et al., 2003]. Deux aspects de ce domaine sont particulièrement intéressants dans le contexte de cette thèse. Tout d'abord, les formalismes synchrones peuvent être vus comme des extensions naturelles des formalismes utilisés pour l'ordonnancement temps réel (les graphes de tâches dépendantes), mais aussi pour la compilation (les représentations single static assignment et les graphes de dépendences de données). Les formalismes synchrones peuvent donc être utilisés comme un terrain d'entente entre ces domaines pour la modélisation formelle. Mais au-delà d'être un terrain d'entente, des travaux existants sur les langages synchrones nous procurent également des techniques efficaces pour la manipulation de structures de contrôle complexes par le biais de ce que l'on appelle les *horloges* et les *retards*.

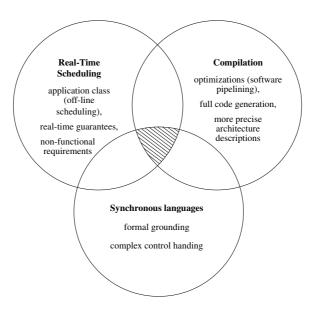

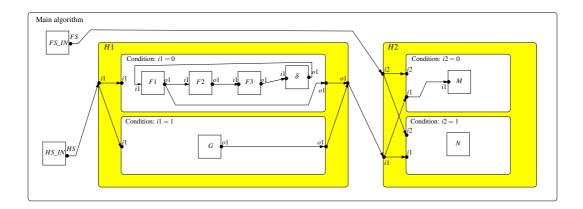

#### **Contribution**

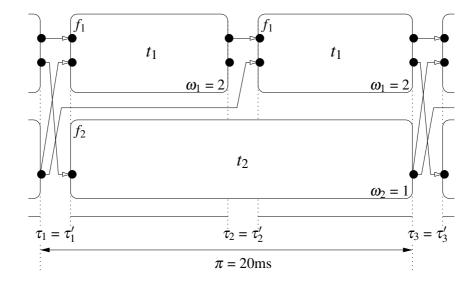

Comme on le voit dans la figure 2, ma thèse s'articule à l'intersection des trois domaines présentés précédemment. Son objectif général est de montrer qu'une meilleure intégration entre ces domaines résulte dans la simplification de la construction de systèmes de contrôle embarqué, et dans une amélioration de leur qualité. Plus précisément, nous montrons que cela est possible pour la classe des systèmes basés sur l'utilisation d'un paradigme d'ordonnancement temps-réel hors-ligne (basé sur des tables). Pour de tels systèmes, nous prenons en compte une technique de compilation avancée (le *software pipelining*) pour améliorer les résultats du processus d'ordonnancement hors-ligne. Notre approche est similaire aux travaux classiques de compilation selon deux autres aspects :

Contrairement aux travaux classiques sur le temps-réel, nous ne nous limitons pas à l'ordonnancement des systèmes, mais permettons la génération complètement automatique de leurs implantations,

Figure 2: Cette thèse se positionne au carrefour entre trois domaines de recherche

Pour préserver l'efficacité et permettre la génération de code notre approche utilise une plateforme d'exécution et des modèles d'applications qui sont plus précis que ceux utilisés dans le domaine de l'ordonnancement temps-réel. En particulier, nous utilisons des formalismes synchrones pour représenter des fonctionnalités complexes et nous permettons la prise en compte de divers types de besoins non-fonctionnels, ce qui permet la modélisation naturelle de tous les besoins d'un cas d'étude avionique.

Cependant, notre travail ne se résume pas simplement à l'application de techniques de compilation à une nouvelle classe de systèmes. En effet, contrairement aux travaux de compilation classiques, notre approche :

- se situe au niveau système, ce qui nécessite une abstraction significative de la plateforme d'exécution,

- fournit des garanties temps-réel dûres, ce qui nécessite une prise en compte sûre du temps,

- considère l'exécution conditionnelle des systèmes,

- considère des besoins non-fonctionnels de différents types, ce qui modifie fondamentalement la nature du problème d'optimisation à résoudre.

La définition de notre approche est basée sur l'adaptation non triviale de concepts, de modèles et d'algorithmes venant des domaines de l'ordonnancement temps-réel, de la compilation et des langages synchrones. Cette adaptation a été facilitée par l'utilisation

de formalismes synchrones qui nous ont fourni un terrain d'entente pour la modélisation et l'analyse des systèmes considérés. Notre travail concerne tous les aspects du problème d'implantation : la conception de formalismes de modélisation, la définition d'algorithmes d'ordonnancement hors-ligne basés sur l'utilisation de tables, et la génération de code exécutable.

Une description détaillée des contributions et de l'originalité de notre travail par rapport aux travaux existants dans les trois domaines de recherche considérés sera fournie lorsque les différents concepts relatifs aux trois domaines auront été introduits (en particulier aux sections 6.1 et 7.1).

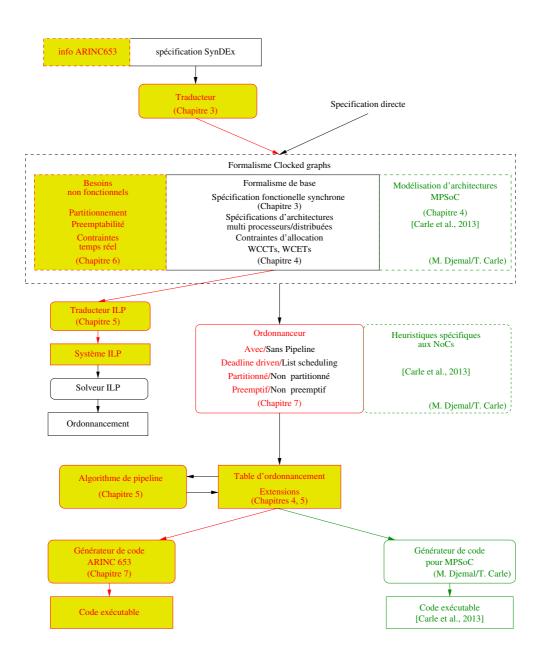

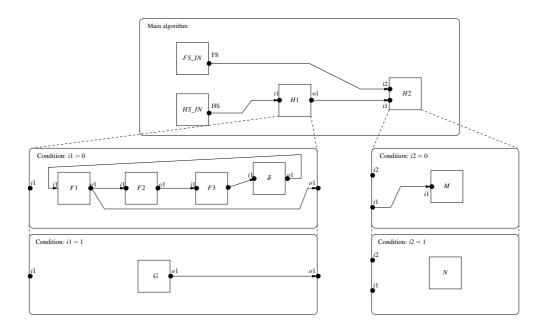

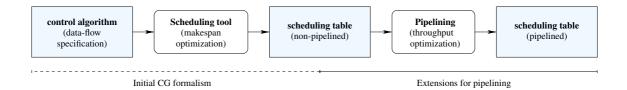

**Organisation de la thèse.** Etant donné que l'objectif de mon travail a été la conception d'une technique de compilation (permettant l'ordonnancement et la génération de code de façon complètement automatisée), celui-ci n'aurait pas été complet sans une évaluation des approches de modélisation, d'ordonnancement et de génération de code que nous fournissons. Pour permettre cette évaluation, les modèles et techniques décrits dans cette thèse ont été accompagnés par leur implantation dans un outil décrit dans la figure 3. Nous appelons cet outil *le compilateur temps-réel LoPhT*<sup>4</sup>.

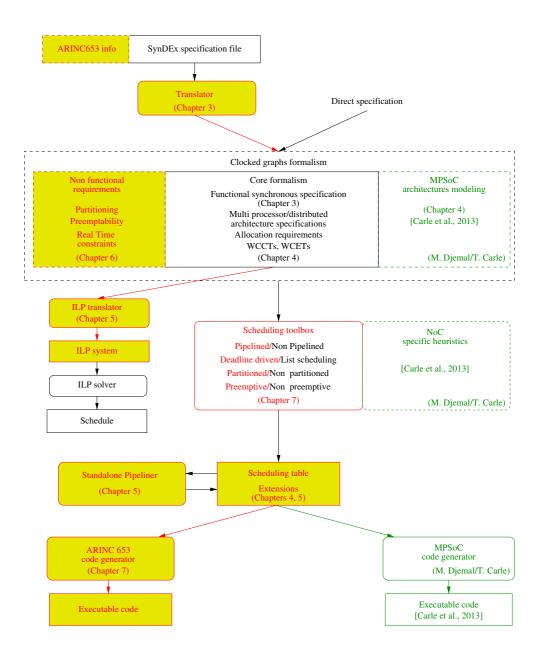

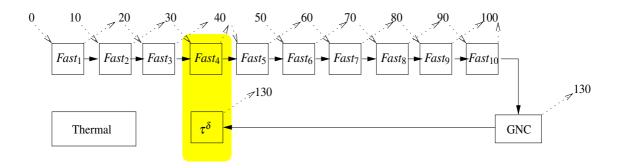

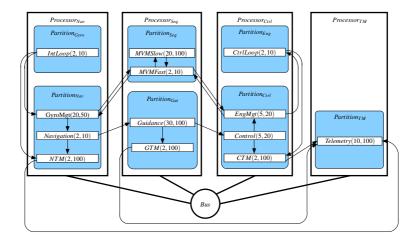

L'organisation de ma thèse suit de près celle de LoPhT, qui est présentée dans la figure 3. C'est pour cela que cette figure est utilisée pour représenter à la fois ma thèse et l'outil LoPhT. Afin d'évaluer la généralité du travail effectué, le compilateur LoPhT a deux cibles : les systèmes partitionés dirigés par le temps qui se conforment au standard IMA/ARINC 653, et les systèmes multiprocesseurs sur puce (MPSoCs) dans lesquels les communications inter-processeurs sont réalisées par le biais d'un réseau sur puce (NoC). Le travail sur les cibles MPSoC a été réalisé en collaboration avec Manel Djemal dans le cadre de sa thèse de doctorat [Carle et al., 2013, 2014] et sera seulement mentionné rapidement dans cette thèse. Dans la figure 3, les éléments en noir sont ceux qui existaient déjà avant le début de ma thèse. Les éléments en rouge (les boites remplies de jaune, ainsi que les éléments à gauche dans la boite "Ordonanceur") sont ceux que j'ai développés lors de ma thèse et qui sont décrits dans ce manuscrit, et les éléments verts (les boites à droite de la figure, contenant la mention M. Djemal/T. Carle) correspondent aux extensions spécifiques aux cibles MPSoC.

Mon manuscrit ne comporte pas un chapitre dédié à l'état de l'art. Cela est dû au fait que ma thèse recouvre trois domaines de recherche ainsi que les relations existant entre eux. Présenter toute l'information correspondante en une fois aurait dégradé la clarté de la présentation. Au contraire, nous fournissons dans le chapitre 2 une introduction aux formalismes synchrones (l'assise formelle de notre approche), puis chaque chapitre technique fournit un état de l'art partiel, souvent regroupé dans une section dédiée (par

<sup>&</sup>lt;sup>4</sup>de l'anglais **Lo**gical to **Ph**ysical **T**ime Compiler : compilateur du temps logique vers le temps physique

Figure 3: Description du compilateur temps-réel LoPhT

exemple les sections 6.1 et 7.1). De cette façon, l'exploration des relations complexes existant entre les modèles et les algorithmes utilisés dans les trois domaines de recherche considérés ne se fait qu'après que ces modèles et algorithmes aient été définis.

Le formalisme utilisé par les algorithmes d'ordonnancement de LoPhT s'appelle Clocked Graphs. Une spécification Clocked Graphs comprend une spécification fonctionnelle et une spécification non-fonctionnelle incluant la définition de l'architecture et des besoins non-fonctionnells de l'application. La spécification fonctionnelle est donnée sous la forme d'un programme flot de données synchrone de bas niveau, écrit dans un langage qui s'appelle également Clocked Graphs. Ce langage synchrone, qui a été défini pour la première fois avant le début de ma thèse, est présenté au chapitre 3. Ce chapitre explore également les relations existant entre ce langage et :

- des formalismes de spécification fonctionnelle de haut niveau. J'y explique comment des programmes synchrones de haut niveau écrits en SynDEx peuvent être transformés en programmes Clocked Graphs,

- les modèles de tâches utilisés pour l'ordonnancement temps-réel. J'y explique comment des programmes synchrones peuvent être abstraits dans des représentations basées sur des systèmes de tâches dépendentes.

Le chapitre 4 présente notre approche de modélisation des ressources de la plateforme d'exécution, ainsi que notre approche de modélisation de l'allocation des ressources, basée sur l'utilisation de tables d'ordonnancement. Ce chapitre définit tout d'abord le formalisme utilisé pour la description des architectures et celui utilisé pour la description des tables d'ordonnancement, tels qu'ils existaient dans LoPhT avant le début de ma thèse. Il inclut également une comparaison rapide entre le modèle de réservation de ressources que nous avons choisi (l'ordonnancement hors-ligne basé sur les tables d'ordonnancement) et d'autres techniques de réservation de ressources, telles que la réservation de bande passante ou l'ordonnancement en-ligne basé sur les priorités.

Le chapitre 5 introduit les extensions que j'ai apportées à ces modèles pour permettre l'application du software pipelining, et pour permettre la modélisation des plateformes MPSoC.

Le chapitre 6 présente la première de nos deux principales contributions techniques : l'utilisation de techniques de software pipelining pour améliorer la qualité des tables d'ordonnancement temps-réel. Ce chapitre inclut un état de l'art approfondi et une section d'évaluation de la méthode.

Le chapitre 7 définit les extensions que j'ai apportées au formalisme Clocked Graphs pour permettre la modélisation de systèmes partitionnés dirigés par le temps incluant des besoins non-fonctionnels complexes. Il inclut une introduction aux systèmes dirigés par le temps (ainsi qu'un état de l'art sur ce sujet).

Le chapitre 8 présente les techniques d'ordonnancement hors ligne et de génération de code capables d'opérer sur les spécifications décrites au chapitre précédent. Finalement, le chapitre 9 conclut ce manuscrit.

#### **Abstract**

There is a long standing separation between the fields of compiler construction and realtime scheduling. While both fields have the same objective - the construction of correct implementations - the separation was historically justified by significant differences in the models and methods that were used. Nevertheless, with the ongoing complexification of applications and of the hardware of the execution platforms, the objects and problems studied in these two fields are now largely overlapping. In this thesis, we focus on the automatic code generation for embedded control systems with complex constraints, including hard real-time requirements. To this purpose, we advocate the need for a reconciled research effort between the communities of compilation and real-time systems. By adapting a technique usually used in compilers (software pipelining) to the system-level problem of multiprocessor scheduling of hard real-time applications, we shed light on the difficulties of this unified research effort, but also show how it can lead to real advances. Indeed we explain how adapting techniques for the optimization of new objectives, in a different context, allows us to develop more easily systems of better quality than what was done until now. In this adaptation process, we propose to use synchronous formalisms and languages as a common formal ground. These can be naturally seen as extensions of classical models coming from both real-time scheduling (dependent task graphs) and compilation (single static assignment and data dependency graphs), but also provide powerful techniques for manipulating complex control structures. We implemented our results in the LoPhT compiler.

## Chapter 1

### Introduction

#### 1.1 Embedded systems design

Embedded systems are computing systems with a dedicated function inside a larger physical or computing system. In this thesis, we are particularly interested in *embedded control systems* [Lee and Seshia, 2011] whose task is to regulate the evolution of (physical) processes in order to ensure their correct functioning. Control and regulation must be understood here in the sense of control theory [Doyle et al., 1990], meaning that an embedded control system is the means of performing the *automatic control* of a *plant* such as a plane, a train, a nuclear reactor, a mobile phone, *etc*.

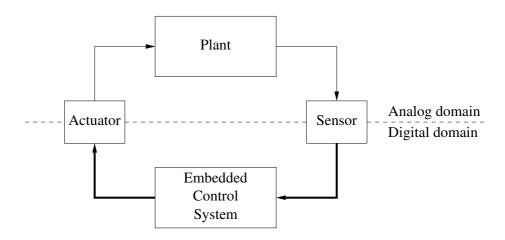

As pictured in Fig. 1.1, an embedded control system interacts with the controlled plant by means of *sensors* and *actuators*. The sensors measure specific (analog) characteristics of the plant and present the resulting information in a discrete form allowing digital treatment by the embedded controller. The discrete output values of the controller are used by the actuators to exert (analog) control over the plant.

For instance, the guidance, navigation, and control (GNC) embedded controller of a

Figure 1.1: Interaction between plant and embedded control system

plane uses a variety of sensors (pressure, temperature, GPS, accelerometers, gyroscopes, *etc.*) to determine its location, speed, and attitude. These values are cyclically used by the GNC controller to manipulate (through actuators) the position of steering controls and the power of thrusters in order to maintain the desired trajectory.

The design of embedded control systems is highly inter-disciplinary. At the top level, it is driven by control engineers and systems engineers. Control engineers provide a specification of the expected behavior of the controller covering functionality and temporal requirements. Defining the functionality of a system consists is specifying which operations must be executed, and in which order, to compute the commands of the actuators starting from the values produced by sensors<sup>1</sup>. But the functional specification alone is not enough to represent the behavior of a control system. To perform effective control, changes in the physical processes of the plant must be followed *in a timely fashion* by changes in actuators. For instance, the GNC embedded controller mentioned above must rapidly react to cross-wind gusts to maintain the stability of the plane, especially during landing phases. For this reason, the attitude control part of the GNC controller is executed once every 50ms [Kent and Williams, 2002].

The specification of these timeliness constraints is realized under the form of *real-time* requirements such as *periods*, *latencies*, *release dates*, *deadlines* attached to the elements of the functional specification. Embedded control systems are therefore *real-time systems* [Butazzo, 2002], which are a sub-class of *reactive systems* [Harel, 1987].

While control engineers are concerned with specifying the behavior of the embedded controller, systems engineers consider the problems of implementing the embedded controller and then providing tools for managing it during its entire lifetime, which is typically of more than 20 years for a commercial aircraft, more than 30 years for a nuclear reactor, more than 150000km on average for a car, etc.. At top level, systems engineering considers macroscopic properties such as cost (in development, maintenance, and possibly disposal), reliability (for both cost and safety reasons), risk, etc. Such macroscopic objectives can be set under the form of non-functional requirements, and systems engineering provides methods for refining such high-level requirements into lower-level requirements such as the ones we consider in this thesis. For instance, Chapter 7 will consider the following requirements coming from systems engineering: the execution platform is already fixed<sup>2</sup>, each operation of the functional specification has been assigned a *criticality*, some operations are *preemptable* and the others are *non-preemptable*, and part of the mapping of the functional specification onto the platform is already fixed. Other non-functional properties that can be considered at this lower level are fault tolerance, energy consumption, evolutivity, etc.

<sup>&</sup>lt;sup>1</sup>The internal state of the system may also be used.

<sup>&</sup>lt;sup>2</sup>Which may also impose some supplementary *real-time* requirements in addition to the ones coming from the control specification.

This is the level where my work takes place: I assume in this thesis that previous engineering phases have produced a functional specification, have fixed the target execution architecture (which can be multiprocessor/distributed), and have provided a set of non-functional requirements including real-time ones. Starting from this input, my objective is to automatically build a correct embedded control system.

Correctness involves here two aspects: functional correctness and the respect of the non-functional requirements. Functional correctness means that the system behaves as prescribed by the functional specification. Ensuring the functional correctness of such a system involves multiple disciplines such as *compilation* (to ensure that each operation of the specification is correctly implemented by a sequential piece of code), *parallel/distributed computing* (for the construction of correct multiprocessor implementation), *etc.* Of particular interest here is the domain of *synchronous language design and implementation* which puts together all the disciplines needed to ensure functional correctness. This is due to the fact that synchronous languages and formalisms, described later in this thesis, were designed specifically to allow the functional specification of embedded control systems. This explains their pervasiveness in embedded systems design and their use in this thesis.

Ensuring the respect of non-functional requirements such as those mentioned above (real-time, criticality, preemptability, power consumption, *etc.*) is mainly studied in the field of *real-time scheduling*, which itself takes advantage of results from hardware design, operating systems design, parallel/distributed computing, fault tolerance, *etc.*

The case for stronger integration. The design of a complex embedded system usually brings together people from all the aforementioned fields. However, in current scientific work and industrial practice the fields remain largely segregated. My opinion is that such a strong segregation results in increased design costs and decreased implementation efficiency, mainly due to 2 causes:

- The interfaces between the various fields, which are usually materialized under the form of model transformations, often abstract away significant details of the source models, which results in efficiency loss. This efficiency loss is often accompanied by the use of unsafe abstractions, which requires validation through extensive tests, and thus increases development costs<sup>3</sup>.

- The lack of communication between the scientific and industrial communities means

<sup>&</sup>lt;sup>3</sup>For instance, tasks models used in real-time scheduling often abstract away all conditional control associated to the tasks, thus adding pessimism to the analysis. Furthermore, many task models used in multiprocessor scheduling assume that communications take no time. For this abstraction to be safe, the worst-case duration of communications should be taken into account by means of overheads added to the durations of tasks. But in most cases, these overheads are not derived from a formal analysis of the communication hardware and protocols.

that some solutions developed in one field will not be applied in another, even when appropriate.

The work of this thesis addresses both points for specific classes of target architectures. To reduce efficiency loss, we use precise models of the application (where conditional control is taken into account), of the platform (where communication costs and the precise execution mechanisms are considered), and of the non-functional requirements, which are adapted to our target execution platforms (time-triggered partitioned systems). Having a precise modeling of the execution platform also reduces the need for unsafe abstractions.

But the main contribution of my thesis is along the second axis. More precisely, I will show that by closely integrating concepts from real-time scheduling, compilation, and synchronous programming, we are able to automatically produce time-triggered real-time implementations that are both correct by construction (thus requiring less validation) and more efficient than those produced by existing approaches. This amounts to applying a compilaton-like approach in the synthesis of real-time implementations from specifications that are complex in both their functional and non-functional aspects. Conversely, this can also be seen as extending the compilation state of the art to take into account non-functional requirements and to allow for a careful accounting of worst-case execution time in compilation.

#### 1.2 Compilation vs. Real-time scheduling

There is a long standing separation between the fields of compiler construction and real-time scheduling. While both fields have the same objective - the construction of correct implementations - the separation was historically justified by significant differences in the models and methods that were used. Indeed, initial work in the compilation community was focused on generating *statically scheduled sequential* machine code. The optimization objective was to improve *average-case speed*, but with *no formal optimality or performance guarantees*. Optimization was based on the *use of detailed microarchitectural information*. Given the nature of the problem it solved, a compiler was expected to *always provide a result* for a syntactically-correct program.

In early real-time multi-tasking systems, compilers were meant to provide the *sequential tasks* that were run by the OS. The system-level design and analysis were the object of the real-time scheduling community. Work on this subject, such as the seminal paper of Liu and Layland [Liu and Layland, 1973], focused on providing *formal schedulability guarantees* for tasks run by a *dynamic/on-line* (*usually priority-preemptive*) *scheduler*. Unlike in compilation, where the objective is the complete synthesis of a piece of code, in real-time scheduling *few or no parameters of the implementation would be synthesized* (*e.g.* the priorities of the tasks, or the allocation of tasks to processors in a distributed

system). Schedulability analysis was based on *coarse abstractions of the tasks and the execution platform*, known as *task models*. Ensuring that such a coarse abstraction is safe is a subject seldom covered in real-time scheduling papers. This was a significant problem in industrial practice, especially given that the system implementation itself remained largely manual (as opposed to the fully automatic compilation, where all aspects of scheduling and code generation were controlled by the compiler). Finally, schedulability analysis could fail.

The differences between the models and methods mentioned above are indeed important and may explain the initial separation of the research and engineering communities. However, both fields have significantly evolved since. When designing compilation techniques for superscalar and VLIW architectures, the compilation community introduced precise timing accounting and the use of multiple, independent execution resources. More recently, it has considered less precise hardware models and more dynamic execution models in order to allow compilation for GPU targets. On the other hand, the real-time scheduling approaches based on *static/off-line*, rather than dynamic/on-line scheduling, gained more importance when industrial needs resulted in the definition of standards such as IMA/ARINC 653 (for avionics systems), AUTOSAR (for automotive systems), or TTA, FlexRay, TTEthernet (for communication buses). Furthermore, systems based on these standards require significant configuration (synthesis), which results in the need for compilation-like approaches handling all aspects of an implementation, and not just the scheduling.

Thus, without becoming indistinct, the types of objects studied by the two communities are today largely overlapping, which should justify a mutualization of the research and engineering effort. Furthermore, in this mutualization process a third research field should play a significant part: the design and implementation of synchronous languages.

As we shall see in the next chapter, the first synchronous languages have been introduced in the real-time community in order to allow the formally sound specification of complex embedded control system. Such systems have large sizes, thus requiring hierarchical modeling, and feature complex control structures, involving concurrency, conditional control, preemption, and stateful behaviors that are not well represented using the very abstract task models. The study of synchronous languages and formalisms became a stand-alone research field, with applications in the specification, formal analysis, and implementation of both embedded systems design and hardware design [Benveniste et al., 2003]. Two particular aspects of this field are appealing from the point of view of this thesis. First of all, synchronous formalisms can be seen as natural extensions of formalisms of both real-time scheduling (the dependent task graphs) and compilation (static single assignment representations and the data dependency graphs). Synchronous formalisms can therefore be used as a common ground for formal modeling. But beyond being a formal

Figure 1.2: This thesis is positioned at the intersection of 3 research fields

ground, previous work on synchronous languages also provides powerful techniques for manipulating complex control structures by means of so-called *clocks* and *delays*.

#### 1.3 Contribution

As pictured in Fig. 1.2, my thesis is developed at the intersection of the 3 research fields presented above. Its most general objective is to show that better integration between these fields allows the easier construction of better embedded control systems.

More precisely, we show that this is possible for the class of systems relying on an off-line (table-based) real-time scheduling paradigm. For such systems, we take into account an advanced compilation technique (software pipelining) in order to improve offline scheduling results. Our approach is similar to classical compilation work in two other aspects:

- Unlike in classical real-time work, we not only perform scheduling, but allow fully automatic generation of the implementation.

- To preserve efficiency and allow code generation our approach uses execution platform and application models that are more precise than those used in real-time scheduling. Particular points here are the use of synchronous formalisms to represent complex functionalities and the ability to consider multiple types of nonfunctional requirements, which allows the natural modeling of all the requirements of an avionics case study.

But our work does not consist in simply applying compilation techniques to a new class of systems. Indeed, unlike in classical compilation work, our approach:

- works at system level, requiring a significant abstraction of the execution platform,

- provides hard real-time guarantees, which in turn requires a safe accouting of time,

- considers conditional (predicated) execution, and

- considers non-functional requirements of various types, which fundamentally changes the nature of the optimization problem that must be solved.

The definition of our approach is based on a non-trivial adaptation of concepts, models, and algorithms of the real-time scheduling, compilation, and synchronous languages fields, which were facilitated by the use of synchronous formalisms to provide a common formal ground for modeling and analysis. Our work covered all aspects of the implementation problem: the design of modeling formalisms, the definition of table-based off-line scheduling algorithms, and the generation of executable code.

A detailed description of the contributions and originality of our work with respect to existing work in the 3 research fields will be provided once the various concepts of the 3 fields will be introduced (and in particular in Sections 6.1 and 7.1).

**Organization of the thesis.** Given that the object of my work has been the design of what is essentially a compiling technique (allowing fully automatic scheduling and code generation), my work would not have been complete without an evaluation of the modeling, scheduling, and code generation approaches we provide. To allow evaluation, all the developments described in this thesis were accompanied by a significant prototyping activity that resulted in the tool flow of Fig. 1.3. We call this tool flow the  $LoPhT^4$  real-time compiler.

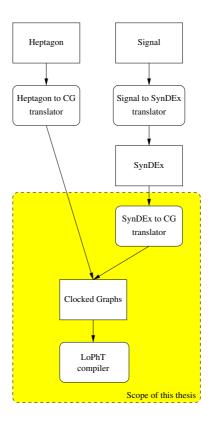

The organization of my thesis closely follows that of the LoPhT tool, presented in Fig. 1.3. This is why we use this figure to detail both. To evaluate the generality of the work, the LoPhT compiler has two targets: partitioned time-triggered systems compliant with the IMA/ARINC653 standard and multiprocessor systems-on-chips (MPSoCs) where interprocessor communication is realized through a network-on-chip (NoC). The work specific to the MPSoC targets was realized in collaboration with Manel Djemal as part of her PhD thesis [Carle et al., 2013, 2014] and will only briefly be mentioned in this thesis. In Fig. 1.3, black elements are those that existed before my thesis started. Red elements (the boxes filled in yellow, as well as the left part of the "Scheduling toolbox" box) are those developed as part of and described in my thesis, and green elements (the boxes

<sup>&</sup>lt;sup>4</sup>For **Lo**gical to **Ph**ysical Time Compiler

Figure 1.3: Tool flow of the LoPhT real-time compiler

in the right part of the figure, labelled with (M. Djemal/T. Carle)) are those corresponding to the MPSoC-specific extensions.

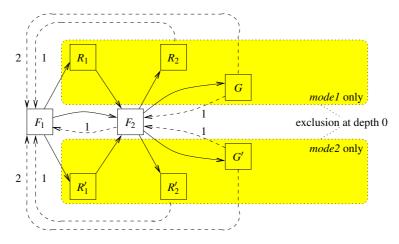

My thesis does not have a single, dedicated state of the art chapter. This is due to the fact that my thesis covers 3 research fields and the relations between them, and presenting this amount of information at once would have compromised the clarity of the presentation. Instead, we provide in Chapter 2 an introduction to synchronous formalisms (the formal basis of our approach) and then, each technical chapter will provide partial state of the art information, often grouped in a dedicated section (such as Sections 6.1 and 7.1). In this way, exploring the complex relationships existing between particular models and algorithms used in the 3 research fields is only done after the models and algorithms are properly defined.

The formalism taken as input by the scheduling algorithms of LoPhT is called Clocked Graphs. A Clocked Graphs specification comprises a functional specification and a nonfunctional specification including the definition of the architecture and that of the nonfunctional requirements. The functional specification part consists in a low-level dataflow synchronous program written in a language that is also called Clocked Graphs. This synchronous language, which was first defined before the beginning of my thesis, is presented in Chapter 3. The chapter also explores the relations between this language and:

- Higher-level functional specification formalisms. I explain here how high-level SynDEx synchronous programs can be translated into Clocked Graphs.

- Task models used in real-time scheduling. I explain here how synchronous programs can be abstracted away as dependent task systems.

Chapter 4 presents our approach to modeling the resources of the execution platform and then our approach to modeling resource allocation (by means of scheduling tables). The chapter first defines the basic architecture description formalism and the basic scheduling table description formalism that existed in LoPhT before the start of my thesis. The chapter also includes a brief comparison between the resource allocation model we chose (table-based off-line scheduling) and other resource allocation techniques, such as bandwidth reservation or on-line priority-based scheduling.

Chapter 5 introduces the extensions I brought to these models to allow the application of software pipelining, and to allow the modeling of MPSoC platforms.

Chapter 6 presents the first of our two main technical contributions, namely our use of software pipelining techniques to improve the quality of real-time scheduling tables. It includes a thorough state of the art and an extensive evaluation section.

Chapter 7 defines the extensions I added to the Clocked Graphs formalism to allow the modeling of partitioned time-triggered systems with complex non-functional requirements. It includes an introduction to time-triggered systems (and a related work on the subject).

Chapter 8 presents the off-line scheduling and code generation technique capable of handling the specifications of the previous chapter. Finally, Chapter 9 concludes.

## Part I

Offline scheduling: fundamental notions and contributions on the specification models for embedded systems

## Chapter 2

## **Introduction to synchronous formalisms**

| $\mathbf{C}$ | on | te | nts |

|--------------|----|----|-----|

|              |    |    |     |

| Contents |        |                                                  |

|----------|--------|--------------------------------------------------|

| 2.1      | The sy | ynchronous model of computation                  |

|          | 2.1.1  | Abstraction issues                               |

|          | 2.1.2  | Clocks and Single-clock synchronous languages 31 |

|          | 2.1.3  | Polychronous languages                           |

|          | 2.1.4  | Languages with affine clocks                     |

|          | 2.1.5  | From logical time to real time                   |

|          |        |                                                  |

#### 2.1 The synchronous model of computation

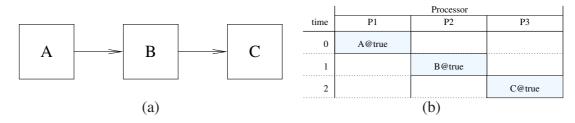

Synchronous languages emerged from the real-time systems community as a way to describe precisely the functional aspects of complex embedded control systems with hard timing constraints [Potop-Butucaru and Sorel, 2014]. This family of languages relies on the *synchronous model of computation* which provides sound formal foundations for describing applications with a cyclic execution model. The synchronous model allows the non-ambiguous representation of behaviors at a high level of abstraction, and then supports formally sound analysis and implementation techniques allowing the synthesis of correct and efficient implementations.

In the synchronous model, the execution of a program is divided into an infinite sequence of execution steps called *reactions* [Benveniste et al., 2003]. The key point of the synchronous model is the *synchrony hypothesis* which states that each reaction happens atomically, as if its computations take zero time [Halbwachs, 1993]. Under this hypothesis, time flows as a sequence of discrete, ordered *instants*, each corresponding to an instantaneous reaction of the system [Potop-butucaru et al., 2005]. Computation instants do not need to be linked to physical time. They just define a sequence of abstract events,

partially or totally ordered by a precedence relation. This is why we say that they define a *logical time* scale.

In the synchronous model, the synchrony between computations of a given instant has a very strong meaning:

- Two reads of the same variable/signal performed during the same instant must always provide the same result, because they happen at the same time.

- If a variable/signal is written during an instant, then all reads will produce this value. Furthermore, no variable/signal should be written twice during an instant, or otherwise it must be specified which of the writes gives the signal/variable its value for the instant.

This property applies to all variables/signals, be them inputs, state variables, or internal variables/signals. Thus, at each instant all the computations of a synchronous model have access to a single, coherent state. No computations occur outside of the time scale defined by the logical instants of the system, the system and its environment being invariant: all changes in the inputs, outputs and in the system state occur only during the logical instants.

The second main tenant of the synchronous model is *causality*. Inside an execution instant, computations take place in zero time, but their execution are performed *causally*, without speculation. Causality amounts to requiring that inside each execution instant the computations can be (partially) ordered so that signal/variable productions precede their reads. In other terms, this amounts to enforcing the respect of the data and control dependencies inside each reaction [Berry, 1996].

Enforcing causality has two important practical consequences: first of all it allows the compilers to automatically detect and reject specifications that cannot be scheduled in a causal way. The second consequence is *functional determinism*: a causal synchronous system will always produce the same outputs when given the same set of inputs. This property is verified by the system regardless of the schedule of the operations, as long as it respects all the dependencies between operations inside each instant.

#### 2.1.1 Abstraction issues

Of course, computations performed by real hardware do take time, which means that synchronous models provide an abstract view of embedded applications. However, current industrial adoption shows that this abstraction level is a good one. We provide here several points justifying (*a posteriori*) this adoption.

As explained above, the synchronous model and the synchronous languages natively include characteristics of embedded control systems: a cycle-based execution model, concurrency, causality.

In conjunction with causality, the synchrony hypothesis provides a strong formal basis for defining well-formed properties that have emerged as good design practices in all fields dealing with the specification and implementation of concurrent behaviors: the absence of races or hazards in software and hardware design, the use of atomic interactions such as transactions, the enforcement of functional determinism. For instance, the development of internal compiler representations such as static single assignment (SSA) had similar objectives. All synchronous formalisms allow simple interpretation in universally recognized mathematical models such as the Mealy machines and the digital circuits. In turn, this allows the use of established formal verification and optimization techniques.

Finally, abstracting away physical time under the form of logical time provides a powerful mechanism of enforcing the separation of concerns between functional aspects of the system on one side, and the real-time non-functional requirements on the other. Indeed, the instantaneity assumption of the *synchronous hypothesis* is interpreted in practice as the capacity of the system to react quickly enough to changes in the physical processes of the controlled plant. In this case, it is not necessary to take into account physical changes occurring between the sensor input and the actuator output.

Furthermore, since computations (conceptually) happen instantaneously, the modeling of an application is independent of the platform on which it will be executed. This means that the application developper can focus on the specification of the functional behaviour of the application, and leave the mapping (distribution) and scheduling of the computations to the compiler or online scheduler.

Mature synchronous languages have been developped and used in both academic and industrial contexts. In the next sections, we will focus on the definition of logical time in synchronous specifications, and how its representation has evolved from a simple model to more complex and expressive forms, as new languages were developped. Our last section briefly presents how real-time constraints can be applied to a synchronous specification, and how this specification can be implemented in a particular case.

#### 2.1.2 Clocks and Single-clock synchronous languages

A key notion in synchronous languages is that of *logical clock*. We saw in the previous section that the synchronous model defines a notion of logical time, where the execution of the system is organized as a set of instants that are partially or totally ordered. At each instant, a reaction of the system is performed. Logical clocks are *totally ordered sets of execution instants*. Logical clocks are used to identify the execution instants where a certain event takes place. In particular, logical clocks are used to determine when the various operations of the system are executed, which means that they are used as *activation conditions* to represent the conditional control of the application. As sets of instants, clocks are partially ordered by the inclusion relation. We say that a clock *c*1 is a sub-clock of

clock c2, denoted  $c1 \le c2$  if the set of instants of c1 is included in that of c2.

The first synchronous languages [Halbwachs et al., 1991, Berry, 1996] only considered systems where execution instants are totally ordered. This set, by itself, is a logical clock, known as the *base clock* of the system. Any synchronous language where each specification has a base clock is classified as a single-clock synchronous language. In single-clock languages, any clock of a program is defined starting from the base clock (by means of predicates, affine relations, *etc.*) and is a sub-clock of the base clock. The synchronous language Clocked Graphs, used in this thesis, is a single-clock synchronous language, and it will be presented in Section 3.2.2.1.

#### 2.1.3 Polychronous languages

For certain embedded control systems, having a single logical time base may not allow a natural description of the system behavior. This happens in systems where various parts need to synchronize on different physical quantities. For example, the ignition control system of a car requires both time-triggered computations for handling the input from the sound sensors, and computations triggered by the engine crankshaft (*i.e.* triggered at certain angles during the rotation of the engine). Defining a base clock from which both the time-triggered and the rotation-triggered clocks are derived can be done for specification purposes, but it imposes artificial relations between the two time bases which must be removed at implementation time. To allow a more natural specification and analysis, languages such as Signal [Guernic et al., 1986, Benveniste and Guernic, 1990, Guernic et al., 2003] and  $\Psi$ C [Chabrol et al., 2009] allow the definition of multiple *independent* time bases on which the various parts of the applications can synchronize. The independent time bases allow different parts of an application to evolve in total temporal independence from one another. These languages are called *polychronous*.

#### 2.1.4 Languages with affine clocks

Some languages such as Giotto [Henzinger et al., 2000] or PRELUDE [Forget et al., 2010] have an intermediate way of representing time bases. These formalisms define multiple time bases, but then relate them in a deterministic way by means of *affine relations* defining frequency (rate, period) and phase relations between them. We call such clocks *affine clocks*. Execution instants of these systems are totally ordered, which would allow their faithful representation using single-clock formalisms. However, using multiple base clocks related in phase and offset allows a more natural description, analysis and code generation of *multi-periodic task systems*.

One particular problem in the synchronous modeling of such systems is the representation of tasks with low period and long duration. Such tasks are not fast enough to be seen as instantaneous in the time base provided by the clocks of tasks of higher period.

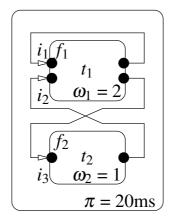

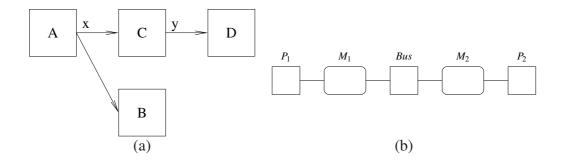

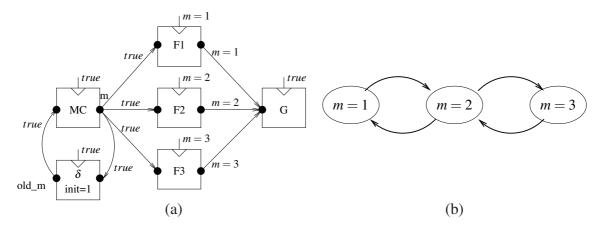

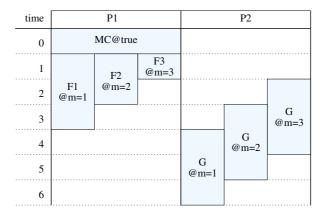

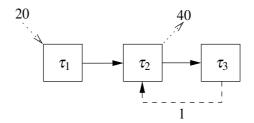

Figure 2.1: Small specification example in the Giotto formalism

In languages based on affine clocks, both time bases (slow and fast) are represented and each task satisfies the synchrony hypothesis in its time base.

Communication and synchronization between tasks belonging to different time bases is deterministic, performed according to rules that take into account the affine relations between clocks. For instance, the Giotto formalism considers that for any given given task t, its outputs are made available in the instant i that follows the one in which t was started, in the time base associated to the clock of t. This means that any other task that starts before i in this model only has access to the previous value of the outputs of t, regardless of its own finishing date. PRELUDE allows a finer control of synchronization by dividing each logical instant into smaller instants and by refining the clocks of the operations that need a finer synchronization. Then the communication semantics are defined using these new, more precise time bases.

## 2.1.5 From logical time to real time

In the synchronous model, clocks are logical time bases, and the synchronous model does not relate clocks to the flow of some physical quantity such as time, length, *etc*. However, when modeling the real-time aspects of an embedded system the clocks offer the natural places where the non-functional information is attached. Indeed, transforming a logical clock into a "physical" one can be as simple as attaching it a period and an offset specified in milliseconds.

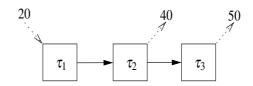

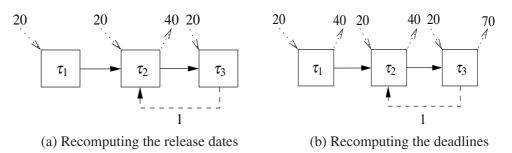

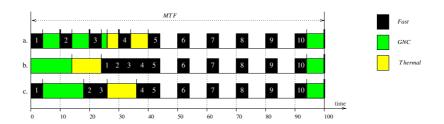

We shall explain how this is done in the Giotto language using the example of Fig. 2.1. Our example specification consists of two Giotto  $tasks\ t_1$  and  $t_2$  grouped in a Giotto module, and which are responsible for the computation of functions  $f_1$  and  $f_2$  respectively. Task  $t_1$  has two outputs, one of which is connected to its own input port  $i_1$ , and the other which is connected to the input port  $i_3$  of task  $t_2$ . Task  $t_2$  has only one output port, which is connected to the second input port of  $t_1$ , named  $t_2$ . The ratio between the activation

Figure 2.2: Time line for a round of execution of the Giotto specification of Fig. 2.1

periods of both tasks imposes that  $t_1$  activates twice as fast as  $t_2$  (as specified by the  $\omega_1$  and  $\omega_2$  parameters).

The system designer imposed a real-time constraint on the module: its execution period must be 20 ms. This constraint is immediately translated into execution periods for the tasks:  $t_2$  will inherit the module period (20 ms) because  $\omega_2 = 1$ , and  $t_1$  will have a period of 10 ms because  $\omega_1 = 2$ . The first release date for each task is by definition 0. The output of a task is made available not at its activation date, but at the next activation date. In a synchronous interpretation, this means that the output of each task is delayed by one instant. Thus, the output of  $t_2$  will be available at dates 20, 40, 60, ..., and the outputs of  $t_1$  at dates 10, 20, 30, ....

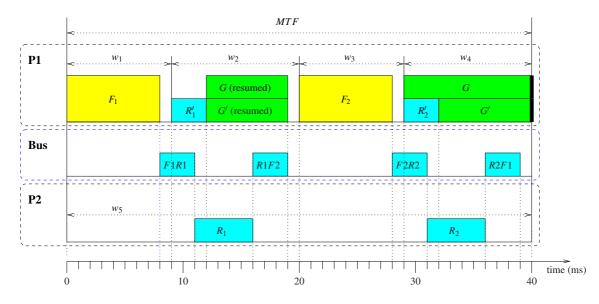

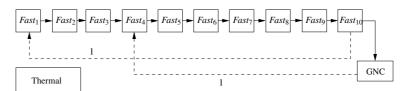

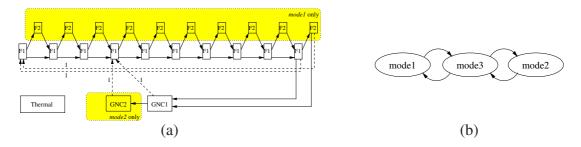

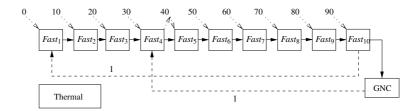

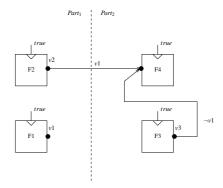

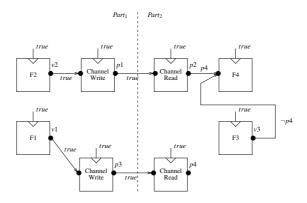

An intuitive view of this execution model is depicted in Fig. 2.2. This figure displays the temporal behaviour of one period of the example application. In this figure, execution instants of task  $t_1$  are started at dates 0, 10, and 20, and execution instants of task  $t_2$  at dates 0 and 20. The outputs produced by the instance of  $t_1$  started at date 0 become available at date 10. The outputs of the first instance of  $t_2$  only become available at date 20. Thus the second instance of  $t_1$  cannot use them even if the actual execution of  $t_2$  completes before date 10.