## Specifying and Verifying Hardware-based Security Enforcement Mechanisms

Thomas Letan

## ▶ To cite this version:

Thomas Letan. Specifying and Verifying Hardware-based Security Enforcement Mechanisms. Hardware Architecture [cs.AR]. CentraleSupélec, 2018. English. NNT: 2018CSUP0002. tel-01989940v2

## HAL Id: tel-01989940 https://inria.hal.science/tel-01989940v2

Submitted on 27 May 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE DE DOCTORAT DE

## CENTRALESUPELEC RENNES

**COMUE UNIVERSITE BRETAGNE LOIRE**

ECOLE DOCTORALE N° 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

## Par Thomas Letan

## Specifying and Verifying Hardware-based Security Enforcement Mechanisms

Thèse présentée et soutenue à Paris, le 25 octobre 2018 Unité de recherche : CIDRE Thèse N° : 2018-06-TH

#### Rapporteurs avant soutenance :

Gilles Barthe Laurence Pierre Professor, IMDEA Software Institute Professeur, Université Grenoble Alpes

#### **Composition du Jury :**

Présidente Emmanuelle Encrenaz Maître de conférences, Sorbonne Université

#### Membres

Gilles Barthe Laurence Pierre Pierre Chifflier Guilaume Hiet Professor, IMDEA Software Institute Professeur, Université Grenoble Alpes Chef de laboratoire, ANSSI Maître de conférences, CentraleSupélec Rennes

Directeur de thèse Ludovic Mé

Professeur, Inria Rennes

Invité Alastair Reid

Researcher, ARM Ltd.

ii

#### Abstract

In this thesis, we consider a class of security enforcement mechanisms we called *Hardware-based Security Enforcement* (HSE). In such mechanisms, some trusted software components rely on the underlying hardware architecture to constrain the execution of untrusted software components with respect to targeted security policies. For instance, an operating system which configures page tables to isolate userland applications implements a HSE mechanism.

For a HSE mechanism to correctly enforce a targeted security policy, it requires both hardware and trusted software components to play their parts. During the past decades, several vulnerability disclosures have defeated HSE mechanisms. We focus on the vulnerabilities that are the result of errors at the specification level, rather than implementation errors. In some critical vulnerabilities, the attacker makes a legitimate use of one hardware component to circumvent the HSE mechanism provided by another one. For instance, cache poisoning attacks leverage inconsistencies between cache and DRAM's access control mechanisms. We call this class of attacks, where an attacker leverages inconsistencies in hardware specifications, *compositional attacks*.

Our goal is to explore approaches to specify and verify HSE mechanisms using formal methods that would benefit both hardware designers and software developers. Firstly, a formal specification of HSE mechanisms can be leveraged as a foundation for a systematic approach to verify hardware specifications, in the hope of uncovering potential compositional attacks ahead of time. Secondly, it provides unambiguous specifications to software developers, in the form of a list of requirements.

Our contribution is two-fold:

- We propose a theory of HSE mechanisms against hardware architecture models. This theory can be used to specify and verify such mechanisms. To evaluate our approach, we propose a minimal model for a single core x86-based computing platform. We use it to specify and verify the HSE mechanism provided by Intel to isolate the code executed while the CPU is in System Management Mode (SMM), a highly privileged execution mode of x86 microprocessors. We have written machine-checked proofs in the Coq proof assistant to that end.

- We propose a novel approach inspired by algebraic effects to enable modular verification of complex systems made of interconnected components as a first step towards addressing the challenge posed by the scale of the x86 hardware architecture. This approach is not specific to hardware models, and could also be leveraged to reason about composition of software components as well. In addition, we have implemented our approach in the Coq theorem prover, and the resulting framework takes advantages of Coq proof automation features to provide general-purpose facilities to reason about components interactions.

Keywords: Security • Hardware Verification • Formal Specification • Formal Methods • Coq

iv

# Remerciements

Je tiens à remercier en premier lieu les membres de mon jury de thèse, à commencer par Gilles Barthe et Laurence Pierre pour avoir rapporté cette thèse. Merci aussi à Emmanuelle Encrenaz-Tiphene et Alastair Reid. Je suis honoré de l'intérêt que vous avez porté à mes travaux.

Je remercie ensuite Ludovic Mé, mon directeur de thèse. Venir te voir à la fin de l'un de tes cours pour te demander s'il n'était pas possible de faire un stage « sur le kernel » aura été avec le recul mon premier vrai pas en direction du monde de la recherche. Merci de m'avoir proposé de rester un an de plus dans l'équipe CIDRE après la fin de mon stage et merci, surtout, de m'avoir parlé de l'ANSSI et encouragé à y postuler. Pierre, Guillaume, votre encadrement et votre soutien tout au long de cette thèse expliquent pour beaucoup sa qualité finale, quand bien même la direction de mes recherches s'est finalement révélée assez éloignée de vos domaines de prédilection. Merci de m'avoir laissé libre d'explorer les sujets qui m'intéressaient. Je n'oublierai jamais comment vous avez su à plusieurs reprises m'expliquer mon propre travail, avec ces mots que je n'arrivais pas à trouver. Merci, donc, à Guillaume Hiet. Début 2013, tu acceptais avec Frédéric Tronel de m'encadrer une première fois pour mon stage de fin d'études. J'étais loin de me douter, alors, que nous travaillerions ensemble aussi longtemps, ni combien notre collaboration m'apporterait. Merci, ensuite, à Pierre Chifflier. Nos discussions pendant ces quatre années ont nourri ma curiosité et forgé mon esprit critique. Te voir t'intéresser à tant de sujets a été une véritable source d'inspiration. Merci, enfin, Benjamin Morin, pour m'avoir fait confiance. L'évolution de ta carrière ne nous a pas permis de travailler ensemble jusqu'au bout de cette thèse, mais je n'oublie pas que c'est en grande partie grâce à toi qu'elle a pu débuter.

Tout au long de cette thèse, j'ai pu compter sur le soutien de beaucoup de personnes. Je tiens ainsi à remercier chaleureusement Yves-Alexis Perez. En ta qualité de chef d'équipe, tu as dû composer avec un agent dont les disponibilités n'étaient pas toujours dépendantes des tâches que tu lui confiais. Si j'ai pu tout à la fois conduire avec succès un travail de thèse et participer aux missions de l'Agence, c'est aussi grâce à toi. J'ai souvent été sensible au temps de recherche que tu me ménageais, à la liberté que tu me laissais pour choisir mes sujets et à la confiance que tu m'as témoignée en me confiant des missions passionnantes. Merci à Arnaud Fontaine. Je n'ai pas oublié notre conversation au Dernier Métro, pendant la rédaction de mon premier article, où nous avons échangé sur mes travaux. Tu as su répondre à mes questions et mettre des mots — qui se retrouvent en filigrane dans tout ce manuscrit — sur mes idées confuses d'alors. Merci à Pierre Néron. Tu m'as énormément aidé à revoir ma copie après le refus de ma première soumission ; tes conseils et relectures ne sont pas étrangers à l'acceptation de mon premier article. Merci aussi à Yann Régis-Gianas d'avoir accepté de me rencontrer pour que je lui présente mes travaux. Ton aide aura été précieuse pour avoir la chance de pouvoir présenter mes travaux à Oxford. Merci à Anaël Beaugnon. Ton soutien, ton aide, tes encouragements m'ont indéniablement aidé à tenir ce marathon qu'est une thèse. Tu t'es toujours spontanément proposée pour relire mes articles et ce manuscrit, quand bien même ils n'étaient pas tout à fait aligné avec ton domaine de recherche. Ton courage et ta ténacité face à l'adversité auront quant à eux été une véritable source d'inspiration. Merci à Marion Daubignard, pour ta gentillesse, ta bonne humeur et tes conseils. J'ai précieusement gardé la citation de ton arrière grand-mère : elle trône encore sur le côté de mon écran. Je la regarde souvent et elle m'aide à me remotiver quand j'en ai besoin. Je ne peux pas ne pas remercier Aurélien Deharbe, qui appréciera je l'espère cette double négation à sa juste valeur. Je suis heureux que nos pérégrinations respectives nous aient amenés à nous rencontrer. J'ai toujours pu compter sur ton soutien, ton énergie et ta bonne humeur communicative quand j'en avais besoin.

Je remercie mes collègues à l'ANSSI. Depuis mon arrivée en octobre 2014, j'ai eu la chance de travailler avec des personnes extrêmement compétentes et passionnées par ce qu'elles faisaient. Vous voir vous investir dans vos missions a nourri ma propre motivation à mener les miennes du mieux possible. J'ai une pensée toute particulière pour ceux avec qui j'ai partagé un bureau. J'en ai déjà cité plusieurs déjà, mais il me faut nommer Alain Ozanne et Philippe Thierry pour être complet. Je remercie aussi chaleureusement l'équipe CIDRE, pour qui je garderai pendant longtemps encore une affection particulière. C'est en vous côtoyant que j'ai découvert le monde de la recherche. La bienveillance et l'investissement dont vous avez tous fait sans cesse preuve forcent le respect. J'ai toujours pris beaucoup de plaisir à vous retrouver et vous présenter l'avancée de mes travaux pendant nos séminaires d'équipe et je regrette seulement ne pas avoir eu l'occasion de le faire plus souvent. J'ai préféré ne pas citer vos noms à tous, car vous êtes trop nombreux. Je me connais et je sais que le risque est grand que j'oublie l'un d'entre vous.

Je ne peux pas conclure ces remerciements sans prendre le temps d'exprimer ma gratitude à ma famille, qui a toujours su répondre présente ; aussi bien dans les petits riens du quotidien que dans les étapes clefs de ma vie. Je crois que je ne mesurerai jamais vraiment tout ce que vous avez fait pour moi. Maman, je crois que je ne t'ai jamais explicitement remercié d'avoir pris la décision de mettre entre parenthèses ta carrière professionnelle pendant si longtemps pour tes enfants. Il m'a fallu longtemps pour prendre la mesure de tout ce que cela représentait. Je profite donc de l'opportunité que m'offre ce manuscrit pour me rattraper. Papa, je t'ai toujours vu redoubler d'efforts pour pourvoir aux besoins des tiens. Tu voulais, toi aussi, t'assurer que tes enfants puissent faire leurs choix de vie, sans regret. Il est ici utile de le dire : vous avez, l'un comme l'autre et l'un avec l'autre, réussit. C'est à nous, maintenant, de tracer le reste de notre route sans jamais oublier la bonne fortune qui fut la nôtre d'être si bien lotis à notre point de départ. N'est-ce pas, Marion, ma petite sœur que j'aime tant ? Merci à toi aussi, évidemment. Je sais que, peu importe ce qui m'arrive, peu importe mes choix de vie, tu seras là.

Enfin, je me tourne vers toi, Juliette, et les mots me manquent pour exprimer toute ma reconnaissance. Pendant la rédaction de ce manuscrit, mais surtout pendant une étape charnière et difficile de ton parcours personnel, tu as toujours cherché à me soutenir, à m'encourager, à me rassurer. J'ai pu me reposer sur ta confiance quand la mienne vacillait. C'est donc tout naturellement que je te réserve mes ultimes remerciements et te dédie ce manuscrit.

# Contents

| Notations<br>Résumé de la thèse |                                            |        |                                               |    |  |  |  |

|---------------------------------|--------------------------------------------|--------|-----------------------------------------------|----|--|--|--|

|                                 |                                            |        |                                               |    |  |  |  |

|                                 | 1.1                                        | Hardy  | ware-based Security Enforcement Mechanisms    | 2  |  |  |  |

|                                 | 1.2                                        | Forma  | al Verification of HSE Mechanisms             | 3  |  |  |  |

|                                 | 1.3                                        | Contr  | ibutions                                      | 4  |  |  |  |

|                                 | 1.4                                        | Outlin | ne                                            | 4  |  |  |  |

| Ι                               | Co                                         | ntext  |                                               | 7  |  |  |  |

| 2                               | Intel x86 Architecture and BIOS Background |        |                                               |    |  |  |  |

|                                 | 2.1                                        | Introc | luction to x86 Architecture                   | 9  |  |  |  |

|                                 |                                            | 2.1.1  | Processor, Architecture and Microarchitecture | 11 |  |  |  |

|                                 |                                            | 2.1.2  | Memories and Cores I/Os                       | 11 |  |  |  |

|                                 |                                            | 2.1.3  | Cache Memory                                  | 14 |  |  |  |

|                                 |                                            | 2.1.4  | Peripherals I/Os                              | 16 |  |  |  |

|                                 |                                            | 2.1.5  | Conclusion                                    | 19 |  |  |  |

|                                 | 2.2 BIOS Overview                          |        |                                               |    |  |  |  |

|                                 |                                            | 2.2.1  | During the boot sequence                      | 19 |  |  |  |

|                                 |                                            | 2.2.2  | At runtime                                    | 20 |  |  |  |

|                                 |                                            | 2.2.3  | HSE Mechanisms Implemented by the BIOS        | 21 |  |  |  |

|                                 | 2.3                                        | BIOS   | HSE Mechanism and Compositional Attacks       | 23 |  |  |  |

|                                 |                                            | 2.3.1  | SMRAM Cache Poisoning Attack                  | 23 |  |  |  |

|                                 |                                            | 2.3.2  | Speed Racer                                   | 25 |  |  |  |

|                                 |                                            | 2.3.3  | SENTER Sandman                                | 25 |  |  |  |

|                                 | 2.4                                        | Concl  | usion                                         | 26 |  |  |  |

| 3                               | State of the Art                           |        |                                               |    |  |  |  |

|                                 | 3.1                                        | Towar  | ds the Formal Verification of HSE Mechanisms  | 28 |  |  |  |

|                                 |                                            | 3.1.1  | Modeling a Hardware Architecture              | 28 |  |  |  |

|                                 |                                            | 3.1.2  | Specifying Security Policies                  | 30 |  |  |  |

#### CONTENTS

|    |                            | 3.1.3 Approaches and Tools                                  | 32 |  |  |  |

|----|----------------------------|-------------------------------------------------------------|----|--|--|--|

|    |                            | 3.1.4 Tour of Existing x86 Models                           | 34 |  |  |  |

|    | 3.2                        | Compositional Verification                                  | 37 |  |  |  |

|    |                            | 3.2.1 Labeled Transition Systems and Components Composition | 38 |  |  |  |

|    |                            | 3.2.2 Process Algebra                                       | 39 |  |  |  |

|    |                            | 3.2.3 Compositional Reasoning for Theorem Provers           | 41 |  |  |  |

|    | 3.3                        | Conclusion                                                  | 43 |  |  |  |

| II | Sp                         | pecifying and Verifying HSE Mechanisms                      | 45 |  |  |  |

| 4  | A Theory of HSE Mechanisms |                                                             |    |  |  |  |

|    | 4.1                        | Theory Definition                                           | 47 |  |  |  |

|    |                            | 4.1.1 Hardware Model                                        | 48 |  |  |  |

|    |                            | 4.1.2 HSE Mechanisms                                        | 49 |  |  |  |

|    |                            | 4.1.3 HSE Mechanism Correctness                             | 54 |  |  |  |

|    |                            | 4.1.4 HSE Mechanisms Composition                            | 57 |  |  |  |

|    | 4.2                        | Case Study: Code Injection Policy                           | 58 |  |  |  |

|    |                            | 4.2.1 Defining Code Injection                               | 59 |  |  |  |

|    |                            | 4.2.2 Code Injection Policy                                 | 60 |  |  |  |

|    |                            | 4.2.3 Code Injection Policy Enforcement                     | 61 |  |  |  |

|    | 4.3                        | Conclusion                                                  | 63 |  |  |  |

| 5  | Spe                        | cifying and Verifying a BIOS HSE Mechanism                  | 65 |  |  |  |

|    | 5.1                        | A Minimal x86 Hardware Model                                | 65 |  |  |  |

|    |                            | 5.1.1 Model Scope                                           | 66 |  |  |  |

|    |                            | 5.1.2 Hardware States                                       | 67 |  |  |  |

|    |                            | 5.1.3 Transition Labels and Transition Relation             | 70 |  |  |  |

|    |                            | 5.1.4 Transition-Software Mapping                           | 73 |  |  |  |

|    | 5.2                        | Specifying and Verifying a BIOS HSE Mechanism               | 74 |  |  |  |

|    |                            | 5.2.1 BIOS HSE Definition                                   | 74 |  |  |  |

|    |                            | 5.2.2 BIOS HSE Mechanism Correctness                        | 77 |  |  |  |

|    |                            | 5.2.3 On SpecCert Machine-Checked Proofs                    | 78 |  |  |  |

|    | 5.3                        | Conclusion                                                  | 82 |  |  |  |

| II | ΙT                         | owards Comprehensive Hardware Models                        | 83 |  |  |  |

| 6  | Mod                        | dular Verification of Component-based Systems               | 85 |  |  |  |

| 0  | 6.1                        | Lessons Learned from MINX86                                 | 85 |  |  |  |

|    | 0.1                        | 6.1.1 MINX86 Limitations                                    | 86 |  |  |  |

|    |                            | 6.1.2       FreeSpec Overview                               | 88 |  |  |  |

|    | 6.2                        | Modeling Programs with Effects                              | 91 |  |  |  |

|    |                            |                                                             |    |  |  |  |

|   |                 | 6.2.1 Interface of Effects                                | 92 |  |  |  |  |  |

|---|-----------------|-----------------------------------------------------------|----|--|--|--|--|--|

|   |                 | 6.2.2 Operational Semantics for Effects                   | 92 |  |  |  |  |  |

|   |                 | 6.2.3 The Program Monad                                   | 94 |  |  |  |  |  |

|   |                 | 6.2.4 Components as Programs with Effects                 | 95 |  |  |  |  |  |

|   | 6.3             | Modular Verification of Programs with Effects             | 97 |  |  |  |  |  |

|   |                 | 6.3.1 Abstract Specification                              | 97 |  |  |  |  |  |

|   |                 | 6.3.2 Compliance and Correctness                          | 99 |  |  |  |  |  |

|   |                 | 6.3.3 Proofs Techniques to Show Compliance for Components | 00 |  |  |  |  |  |

|   | 6.4             | Conclusion                                                | 03 |  |  |  |  |  |

| 7 | Con             | clusion and Perspectives 1                                | 05 |  |  |  |  |  |

|   | 7.1             |                                                           | 06 |  |  |  |  |  |

|   | 7.2             |                                                           | 06 |  |  |  |  |  |

|   |                 |                                                           |    |  |  |  |  |  |

| Α |                 | A Formal Definition of HSE Mechanisms in Coq 10           |    |  |  |  |  |  |

|   | A.1             |                                                           | 09 |  |  |  |  |  |

|   |                 | A.1.1 Definition                                          | 09 |  |  |  |  |  |

|   |                 |                                                           | 10 |  |  |  |  |  |

|   |                 |                                                           | 11 |  |  |  |  |  |

|   | A.2             | HSE Mechanisms                                            | 12 |  |  |  |  |  |

|   |                 |                                                           | 12 |  |  |  |  |  |

|   |                 | A.2.2 Trace Compliance                                    | 13 |  |  |  |  |  |

|   |                 | A.2.3 HSE Mechanism Correctness                           | 15 |  |  |  |  |  |

|   |                 | A.2.4 HSE Mechanisms Composition                          | 16 |  |  |  |  |  |

|   | A.3             | Case Study: Code Injection Policies 1                     | 19 |  |  |  |  |  |

|   |                 | A.3.1 The Software Stack                                  | 19 |  |  |  |  |  |

|   |                 | A.3.2 Code Injection                                      | 20 |  |  |  |  |  |

|   |                 | A.3.3 Code Injection Policies                             | 20 |  |  |  |  |  |

| B | Publications 12 |                                                           |    |  |  |  |  |  |

|   | <b>B</b> .1     | Peer-reviewed Conferences 1                               | 23 |  |  |  |  |  |

|   | B.2             | Free Software                                             | 23 |  |  |  |  |  |

|   | B.3             | Seminar                                                   | 23 |  |  |  |  |  |

#### CONTENTS

х

# NOTATIONS

**Constructors** We often define sets of values in terms of functions to construct these values. These functions are called "constructors," and they have mutually exclusive images, i.e. it is not possible to construct the same value with two different constructors. Constructor names begin with a capital letter. We adopt a notation similar to Haskell sum types to define sets *via* constructors. For instance, this is how we define the disjoint union operator  $\forall$ :

$$\begin{array}{rcl} A \uplus B & \triangleq & Left : A \to A \uplus B \\ & & | & Right : B \to A \uplus B \end{array}$$

Given  $a \in A$ , we write  $Right(a) \in A \uplus B$  for the injection of a inside  $A \uplus B$ .

**Named Tuples** We adopt a notation similar to Haskell record types to manipulate "named" tuples, that is tuples where each component is a field identified by a name.

$$\mathsf{T} \triangleq \langle \text{ field}_1 : \mathsf{A}, \quad \text{field}_2 : \mathsf{B} \rangle$$

For  $x \in T$ , we write *x*.*field*<sub>1</sub> for selecting the value of the *field*<sub>1</sub> field. We write  $x\{field_i \leftarrow a\}$  for updating the value of the field *field*<sub>i</sub>. As a consequence,

$$x{field_i \leftarrow a}.field_k = \begin{cases} a & \text{if } k = i \\ x.field_k & \text{otherwise} \end{cases}$$

We use a similar notation for functions, that is given  $f : A \to B$ ,  $f\{x \leftarrow y\}$  is a new function such that

$$\forall z \in A, f\{x \leftarrow y\}(z) = \begin{cases} y & \text{if } z = x \\ f(z) & \text{otherwise} \end{cases}$$

Finally, we ease the definition of nested updates by gathering nested fields on the left side of  $\leftarrow$ . Let  $R \triangleq \langle s : T \to U, v : W \rangle$  be a set of named tuples whose field s is a function which maps elements of T to element of U. To replace the value associated to  $t \in T$  by  $u \in U$  in the function associated with the field s of  $r \in R$ , we write  $r\{s(t) \leftarrow u\}$  instead of  $r\{s \leftarrow r.s\{t \leftarrow u\}\}$ .

#### NOTATIONS

xii

# Résumé de la thèse

Dans le cadre de cette thèse, nous nous intéressons à une classe particulière de mécanismes de sécurité. Ces mécanismes nécessitent qu'un ou plusieurs logiciels de confiance configurent la plate-forme matérielle afin de contraindre l'exécution du reste de la pile logicielle à respecter une politique de sécurité donnée. Nous qualifierons par la suite de mécanisme HSE (de l'anglais *Hardware-based Security Enforcement*) les instances de cette classe. L'utilisation par le système d'exploitation des mécanismes de pagination pour isoler chaque application est sûrement l'exemple le plus courant de la mise en pratique d'un mécanisme HSE.

#### Contexte

Le contournement d'une politique de sécurité normalement assurée par le biais d'un mécanisme HSE peut s'expliquer par une erreur dans sa mise en œuvre, aussi bien dans l'un des logiciels de confiance chargés de sa configuration que dans les mécanismes matériels sur lesquels il se repose. Nous nous sommes intéressés à ce second cas, et plus spécifiquement encore au problème des erreurs affectant les spécifications de la plate-forme. Cette dernière est composée de plusieurs dizaines de composants interagissant ensemble et la complexité résultante de ces interactions rend en pratique difficile la conception d'un mécanisme à visée sécuritaire. Pour chaque nouvelle fonctionnalité que le concepteur de la plate-forme désire ajouter, il est nécessaire de s'assurer (1) qu'elle n'interfère pas avec les mécanismes HSE existants et (2) qu'il n'est pas possible de la contourner par le biais d'une fonctionnalité antérieure. Ces risques peuvent être critiques pour la sécurité de la plate-forme comme l'illustre l'attaque SENTER Sandman présentée en 2015 par Xeno Kovah et al. [1]. Les auteurs ont montré qu'il était possible de modifier le contenu de la mémoire flash d'un ordinateur en utilisant une extension de l'architecture x86 nommée Intel TXT [2]. Ils ont en effet remarqué que l'instruction SENTER permettait — dans sa première version — de désactiver une composante essentielle du mécanisme de protection en intégrité de la mémoire flash.

La multiplication des chemins d'attaque potentiels liée au nombre grandissant des composants constitue une menace clairement identifiée dans la littérature [3]. Dans le cas particulier des mécanismes HSE, les vulnérabilités successives affectant l'architecture x86 [4, 5, 6, 7, 1] ont été caractérisées par une sévérité très importante, car ces mécanismes visent à assurer l'isolation des couches les plus basses — et, par voie de conséquence, les plus privilégiées — de la pile logicielle.

#### Objectifs

Dans cette thèse, nous avons cherché à proposer une approche rigoureuse pour spécifier et vérifier, par le biais de méthodes formelles, des mécanismes HSE. Notre hypothèse de départ est qu'une telle approche bénéficierait à la fois aux concepteurs des plates-formes matérielles et aux développeurs de logiciels qui s'appuient sur les mécanismes matériels de ces plates-formes. Les premiers pourraient vérifier que leurs mécanismes matériels permettent effectivement de mettre en œuvre les politiques de sécurité visées. Quant aux seconds, ils pourraient profiter de spécifications décrivant sans ambiguïtés les exigences auxquelles leurs logiciels doivent se conformer pour pouvoir profiter de ces politiques.

Notre démarche se place à la croisée de deux domaines de vérification. La vérification matérielle, d'une part, se concentre généralement sur des propriétés qui s'appliquent inconditionnellement à la plate-forme comme à la pile logicielle exécutée par cette dernière. De nombreux travaux ont ainsi cherché à vérifier des protocoles de cohérence de caches [8, 9], ou la correction de l'implémentation d'un modèle mémoire par un processeur [10]. La vérification de logiciels bas niveaux, notamment des systèmes d'exploitation ou des hyperviseurs, se repose naturellement sur des modèles de la plate-forme matérielle sous-jacente. Néanmoins, ces modèles abstraient bien souvent autant que faire se peut la complexité de l'architecture matérielle, pour n'en garder que les éléments essentiels — bien souvent, les mécanismes de pagination et les interruptions. La conséquence de cet état de fait est que les mécanismes nécessitant une configuration logicielle sont moins souvent les sujets de vérification formelle.

Les travaux qui se rapprochent le plus de notre objectif et dont nous avons connaissance sont ceux de Jomaa *et al.* [11], en lien avec le protokernel Pip [12]. Nous nous inscrivons dans la continuité de cette approche, mais cherchons à dégager un formalisme beaucoup plus générique, qui reposerait notamment sur un modèle matériel le plus générique possible. Cependant, un tel modèle n'est pas sans poser de sérieux défis quant à son applicabilité dans un problème de vérification réaliste. En effet, la complexité d'un modèle a un impact direct sur la facilité avec laquelle on peut l'exploiter. Il est donc important de se poser, en amont, les bonnes questions quant à l'approche utilisée pour le définir, afin que les efforts nécessaires pour sa conception ne soient pas dépensés en vain. Plusieurs travaux ont plaidé en faveur d'une approche basée sur un raisonnement par composition (*compositional reasoning* en anglais), où le système est divisé en un sous-ensemble de composants et la vérification axée autour de leurs interactions, pour faire face à ces défis [13, 14].

#### Contributions

Dans cette thèse, nous présentons deux contributions complémentaires, qui ont chacune fait l'objet d'une publication à la conférence *Formal Methods*; d'abord en 2016 [15], puis en 2018 [16].

**Une théorie des mécanismes HSE.** Notre première contribution est une théorie des mécanismes HSE, dont l'objectif premier est de servir de support à la spécification et à la vérification de ces derniers. Elle s'articule autour d'une méthodologie divisée en plusieurs étapes. L'architec-

xiv

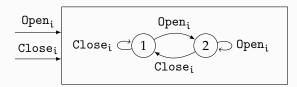

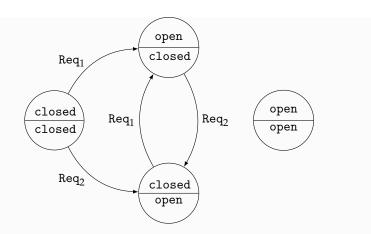

ture matérielle est dans un premier temps modélisée sous la forme d'un système de transitions étiquetées (*labeled transition system*, en anglais, désigné par la suite par l'acronyme LTS). Un LTS est traditionnellement caractérisé par un ensemble d'états, un ensemble d'étiquettes et une relation de transition. Une étiquette est attachée à chaque transition pour permettre de leur donner une sémantique particulière. Le plus souvent, l'étiquette permet de décrire ce qui a causé la transition.

Une trace d'un LTS est une séquence potentiellement infinie de transitions et décrit un comportement possible du système. Dans le cas qui nous intéresse, une trace décrit une exécution d'une pile logicielle par la plate-forme. La formalisation de politiques de sécurité pour des systèmes de transitions est désormais bien établie. Ces politiques peuvent être formellement définies sous la forme de prédicats de traces [17, 18, 18, 19] ou, dans les cas les plus complexes, d'ensemble de traces [20].

Un modèle matériel se présente sous la forme d'un quadruplet  $\langle H,L_S,L_H,\to\rangle$  dans notre théorie, où :

- H est l'ensemble des états que peut prendre le LTS, par exemple la valeur des registres des différents composants matériels de la plate-forme et le contenu de la DRAM;

- L<sub>S</sub> est l'ensemble des étiquettes attachées aux transitions dites logicielles, qui sont une conséquence directe et prévisible de l'exécution, par la plate-forme matérielle, d'une instruction faisant partie du programme d'un logiciel;

- L<sub>H</sub> est l'ensemble des étiquettes attachées aux transitions dites matérielles;

- $\rightarrow$  est la relation de transition du système.

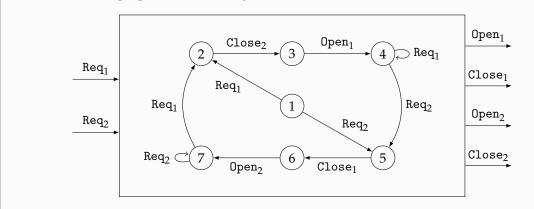

En nous basant sur ce type de modèle matériel, nous pouvons spécifier un mécanisme HSE sous la forme d'un ensemble de logiciels de confiance chargés d'implémenter ce mécanisme et d'exigences qu'ils doivent respecter pendant leurs exécutions. À partir de cette définition, il est possible de dégager un sous-ensemble de traces du modèle matériel dans lesquelles les logiciels de confiance ont correctement implémenté le mécanisme HSE étudié, en respectant à tout moment les deux exigences. Par la suite, un mécanisme HSE peut être prouvé correct vis-à-vis de la politique de sécurité qu'il cherche à mettre en œuvre, si le sous-ensemble des traces du modèle matériel qui le caractérisent satisfait le prédicat formalisant la politique.

Nous avons déroulé notre méthodologie sur un exemple réel, à savoir le mécanisme Hardware-based Security Enforcement (HSE) implémenté par le BIOS des plates-formes x86 pour isoler leur exécution de celles des logiciels appartenant au reste de la pile logicielle. Le BIOS (*Basic Input/Output System*) est un composant logiciel fourni par le constructeur de la plate-forme, dont le principal objectif est d'initialiser puis de maintenir cette dernière en état de fonctionnement. Ce mécanisme HSE repose sur des fonctionnalités matérielles relativement peu connues, notamment un contexte d'exécution particulier des processeurs d'Intel — au même titre que les *rings*, par exemple — nommé le *System Management Mode* (SMM). Le SMM a ceci d'intéressant qu'il est le contexte d'exécution le plus privilégié de l'architecture x86, si bien qu'une escalade de privilège permettant d'exécuter du code malveillant en SMM peut avoir des conséquences désastreuses pour la sécurité de la plate-forme. Malheureusement, il a été l'objet en dix ans de plusieurs vulnérabilités profitant d'incohérences dans les différents composants matériels impliqués dans son isolation [4, 5, 6]. Parce que le SMM et les autres mécanismes matériels impliqués dans le mécanisme HSE qui nous intéresse ne sont pas pris en compte dans les modèles x86 de notre connaissance, nous avons dû en définir un nouveau. Cette démarche s'est révélée riche d'enseignement quant aux propriétés qu'un modèle générique d'une plate-forme matérielle devrait exhiber pour que ce dernier demeure utilisable dans un processus de vérification. La modularité, tant de la modélisation que du travail de vérification est, de notre point de vue, l'élément clef à privilégier pour pouvoir accompagner au mieux un passage à l'échelle.

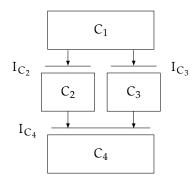

**Raisonnement par composition pour Coq.** Le raisonnement par composition permet de vérifier chaque composant d'un système complexe en isolation, en spécifiant des hypothèses sur le comportement du reste du système d'une part et en s'assurant que le composant adoptera bien un comportement attendu en retour. Une fois cette première étape réalisée pour chaque composant, il devient possible de raisonner sur la composition de chacun des éléments : si le comportement garanti pour un composant  $C_1$  satisfait les hypothèses de raisonnement d'un second composant  $C_2$ , alors il est possible de conclure que la composition de  $C_1$  et de  $C_2$  garantit le comportement de  $C_2$ .

Notre seconde contribution est une approche permettant la conduite de raisonnement par composition sur des composants modélisés grâce à un langage purement fonctionnel [16] ainsi qu'une implémentation nommée FreeSpec de cette approche [21] dans l'assistant de preuve Coq [22]. L'originalité de notre contribution est de mettre à profit des paradigmes fonctionnels — les monades [23], les effets algébriques et les *handlers* d'effets [24] — pour les appliquer au domaine de la vérification de plates-formes matérielles. Les modèles écrits dans notre formalisme sont facilement lisibles et soulignent bien les connexions entre les différents composants. De plus, nous avons implémenté des tactiques dédiées permettant d'automatiser en partie l'exploration de ces modèles, ce qui facilite grandement le travail de vérification.

Rien ne cantonne cependant le résultat de ce travail à la vérification de mécanismes HSE. Il peut ainsi tout à fait s'appliquer dans le cadre de la vérification d'un système purement logiciel, dès lors que ce logiciel peut être décrit sous la forme de plusieurs composants interagissant ensemble. La principale limitation de notre approche tient dans les contraintes que nous imposons aux interconnexions des composants du système. En l'état, FreeSpec ne permet par exemple pas de considérer des graphes qui contiennent des cycles ou des « arêtes en avant » (*forward edges* en anglais). Cette contrainte est importante, mais dans la pratique, nous avons constaté qu'il est possible d'étudier une architecture matérielle à un niveau de détail où les composants s'organisent en arbre, selon une hiérarchie par couches successives.

#### Travaux futurs

La suite logique de nos travaux serait d'appliquer le formalisme de FreeSpec dans le cadre de

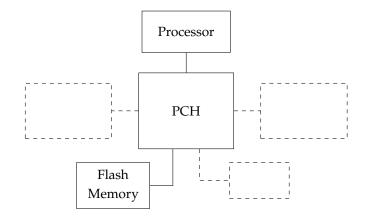

la vérification complète d'un mécanisme HSE par le biais de notre théorie. Par exemple, nous pourrions remplacer le modèle matériel que nous avons développé pour spécifier et vérifier le mécanisme HSE implémenté par le BIOS et juger l'impact que cela aurait sur le travail de vérification. Nous ne doutons par ailleurs pas que les limitations actuelles de l'approche que nous proposons avec FreeSpec se heurteront à la complexité inhérente aux architectures matérielles. Les résoudre nous permettrait d'envisager le passage à l'échelle et donc la définition d'un modèle x86 générique, pouvant servir de support à une large collection de mécanismes HSE couramment implémentés par les couches basses de la pile logicielle. Cela poserait très vite la question de la confiance que l'on peut placer dans un tel modèle et notamment son adéquation avec ce qui est réellement implémenté par le matériel. La validation de modèle est un problème de recherche à part entière. Dans notre cas, elle est rendue plus complexe par le fait que beaucoup de composants matériels sont fortement intégrés à la plate-forme matérielle et difficilement accessible séparément. C'est par exemple le cas du Platform Controller Hub (PCH), le composant matériel qui fait l'intermédiaire entre le processeur et les périphériques les moins demandant en vitesse d'accès. Ce dernier est maintenant directement intégré directement dans la puce des processeurs Intel.

RÉSUMÉ DE LA THÈSE

xviii

# 1

## INTRODUCTION

"All problems in computer science can be solved by another level of indirection."

David Wheeler

To manage complexity, computing platforms are commonly built as successions of abstraction layers, from the hardware components to high-level software applications. Each layer leverages the interface of its predecessor to expose a higher-level, more constrained set of functionalities for its successors. This enables separation of concerns —each layer encapsulates one dimension of the overall complexity— and modularity —two layers which expose the same interface can be seamlessly interchanged.

From a security perspective, each layer is often more privileged than its successors. For instance, system software components (*e.g.* an Operating System (OS) or a hypervisor) manage the life cycle of upper layers (*e.g.* applications or guest OSes). In such a context, one layer implicitly trusts its predecessors. On the one hand, it is important to keep this fact in mind when we consider the security of the computing platform. Trust in lower levels of abstraction can be misplaced, *e.g.* hardware implants and backdoors pose a significant threat to the platform security [25], and the platform firmware has been used as a persistent attack vector across machine restarts [26]. On the other hand, one layer may constrain the execution of its successors, with respect to a targeted security policy, *e.g.* an OS enforces availability —fair share of processor time—, confidentiality and integrity —exclusive partition of physical memories— properties for the applications it manages. Concerning the lowest layers of software stack, *e.g.* the Basic Input/Output System (BIOS) and system software components, the common approach is to rely on features provided by the hardware architecture to reduce the hardware capabilities that can be used by upper layers. This scenario characterizes a class of security mechanisms we call HSE mechanisms.

In the following, we first detail in more detail how HSE mechanisms are implemented and which threats these implementations face. In this thesis, we aim to specify and verify HSE

mechanisms. We motivate this choice, then give a brief overview of our contributions. We conclude this first Chapter with a brief summary of the outline of this manuscript.

#### 1.1 Hardware-based Security Enforcement Mechanisms

A HSE mechanism consists of the configuration by a trusted software component of the underlying hardware architecture in order to constrain the execution of untrusted software components with respect to a targeted security policy. For instance, system software components often leverage, among other mechanisms, a Memory Management Unit (MMU) to partition the system memory, and therefore needs to setup so-called page tables. Thus, when an application is executed, it can only access a subset of the system memory. Besides, the processor can leverage a hardware timer to stop applications execution, without the need for these applications to cooperate.

A HSE mechanism enforces its targeted security property when (1) the trusted software components correctly configure the hardware features at their disposal, and (2) these features are sufficient to constrain the untrusted software execution as expected. Both requirements remain challenging and have been violated at many occasions in the past, due to software and hardware errors alike.

**Software Errors.** Part of vulnerabilities in HSE mechanism implementations by trusted software components are due to some misuse of hardware features [27]. In the past, most lower-level pieces of software, such as firmware components, have not been conceived and implemented with security as primary focus. The increasing complexity of hardware architectures can also be held partly responsible. While computers are made of dozens of components, software developers have to read and understand as many, independent and often large documents of various forms (*e.g.* data sheets, developer manuals), and they rarely focus on security. When software developers misunderstand the documentation, as it happened for instance for the mov ss and pop ss x86 instructions [28], the impact in terms of security can be significant.

**Hardware Errors.** Over the past decades, vendors have regularly added security features to their products. Intel, for instance, has notably introduced hardware-based virtualization (VT-x, VT-d) [29], dynamic root of trust (TXT) [2], or applicative enclaves (SGX) [30, 31]. It is crucial to notice that most of them have been circumvented due to implementation bugs [32, 33]. This is not surprising, as novel hardware features tend to be more and more complex. In extreme scenarios, novel hardware features have been turned into attack vectors [32]. In addition to these implementation errors, the fact that hardware architectures often comprise hundreds of features implemented by dozens of interconnected devices complicates the conception of new hardware features. Indeed, these new features should not interfere with the security properties enforced by the existing components of the platform. For instance, the flash memory (where lives the BIOS code) is supposedly protected against arbitrary write accesses from system software components, thanks to a particular hardware interrupt. When Intel introduced

#### 1.2. FORMAL VERIFICATION OF HSE MECHANISMS

TXT [2], they did not anticipate that this novel security feature had the particular side effect of disabling the hardware interrupt used to protect the flash memory [1]. Such inconsistencies in hardware specifications pave the road toward compositional attacks [3]. Compositional attacks characterize scenarios where each component is working as expected in isolation, yet their composition creates an attack path which prevents end-to-end security enforcement. In the context of HSE mechanisms, this means untrusted software components can leverage one hardware component to defeat a HSE mechanism implemented to constrain its execution. Compositional attacks are due to a flaw in the specifications of the computing platform. As such, they precede implementation errors, and their countermeasures often require a change in the hardware interface. To prevent them, it is mandatory to reason about the computing platform as a whole.

#### **1.2 Formal Verification of HSE Mechanisms**

The significant impact of previously disclosed compositional attacks [4, 5, 6, 7, 1] motivate our desire to formally specify and verify HSE mechanisms. We believe this would benefit both hardware designers and software developers. Firstly, a formal specification of HSE mechanisms can be leveraged as a foundation for a systematic approach to verify hardware specifications. For each novel hardware feature introduced, it is necessary to check that the previous proofs hold, meaning this feature does not introduce any compositional attack. Secondly, it provides unambiguous specifications to firmware and system software developers, in the form of a list of requirements to comply with, and the provided security properties. We believe these specifications are a valuable addition to the existing documentation, because they gather at one place information that is normally scattered across many documents which sometimes suffer from lack of security focus.

We steer a middle course between two domains: hardware and system software verification. Generally, hardware verification focuses on properties that are transparent to the executed software, and require no configuration from its part, while software verification abstracts as much as possible the hardware architecture complexity. However, compositional attacks can come from unsuspected places, with no apparent link with the considered security mechanism. For instance, the SENTER Sandman attack [1] leveraged a dedicated execution mode of x86 processor to disable the protection of the flash memory wherein the BIOS code is stored. Hence, the composition of the numerous configurable hardware features is less subject to formal verification. At the same time, some components are individually complex: for example, the Intel Architectures Software Developer Manual [34] is 4842 pages long, the Memory Controller Hub datasheet [35] is 430 pages long, and the Platform Controller Hub datasheet [36] is 988 pages long. Besides, new hardware components and new versions of already existing components are frequently released. As a consequence, the more modular our models and proofs are, the more practicable our approach becomes. Otherwise, each modification of the hardware architecture will have an important impact on the proofs already written.

#### **1.3 Contributions**

During the first stage of this thesis, we propose a theory of HSE mechanisms in the form of requirements trusted software components have to satisfy. A HSE mechanism is correct if its requirements are sufficient to make the hardware architecture enforce a targeted security policy. To evaluate our approach, we formally specify and verify a HSE mechanism implemented by the BIOS of x86-based computing platform at runtime to remain isolated from the rest of the software stack. Our choice has been motivated by the prominent position of the Intel hardware architecture on the personal computer market. Moreover compositional attacks targeting this architecture have been disclosed [4, 5, 6, 7, 1]. The resulting model assumes as little as possible about the actual implementation of the BIOS, and constitutes, to the extent of our knowledge, the first formalization of the BIOS security model at runtime. Our model and its related proofs of correctness have been implemented in the Coq theorem prover, to increase our confidence in our result. This work has been presented at the 21<sup>th</sup> International Symposium on Formal Methods (FM2016) [15]. In addition, the resulting project, called SpecCert, has been made available as free software [37].

After this first contribution, we focus our attention on the challenge posed by the modeling of a complex hardware architecture like the x86 architecture. In this thesis, we advocate for the use of a general-purpose model of a hardware architecture to support the specification of HSE mechanisms which can be implemented on this architecture. Our experiment with our theory of HSE mechanisms convinced us that such a general-purpose model should obey certain requirements, notably in terms of readability and modularity, so it could remain applicable to real-life verification problem. Our second contribution is a novel approach, inspired by algebraic effects, to enable modular verification of complex systems made of interconnected components. This approach is not specific to hardware models, and could also be leveraged to reason about composition of software components as well. This work has been presented at the 22<sup>th</sup> International Symposium on Formal Methods (FM2018) [16]. Besides, we have implemented our approach in Coq, and the resulting framework, called FreeSpec, takes advantages of theorem prover automation features to provide general-purpose facilities to reason about components interactions. Similarly to SpecCert, FreeSpec has been published as free software [21].

#### 1.4 Outline

The rest of this manuscript proceeds as follows.

First of all, Part I provides the context in which this thesis falls. In Chapter 2, we give an introduction to the x86 hardware architecture and the particular role played by the BIOS, in order to present three illustrative compositional attacks. In Chapter 3, we review existing formal verification approaches that have been proposed to verify hardware and software systems. We justify, in this context, our choices in terms of formalism and tools.

Part II focuses on our first contribution. In Chapter 4, we present our general-purpose theory to support the specification and verification of HSE mechanisms. In Chapter 5, we leverage this

#### 1.4. OUTLINE

theory to reason about the HSE mechanism implemented by the BIOS to remain isolated from the rest of the software stack at runtime.

Part III focuses on our second contribution. In Chapter 6, we present our compositional reasoning framework for Coq, to modularly specify and verify systems made of interconnected components

Finally, we conclude this thesis in Chapter 7, where we suggest some possible directions for future work.

## Part I

# Context

2

## INTEL x86 Architecture and BIOS Background

"You're building your own maze, in a way, and you might just get lost in it."

- Marijn Haverbeke

From a market share perspective, the x86 hardware architecture is widely used for laptops, desktops and servers. Intel has introduced several security features to support HSE mechanism over the past decades: hardware-based virtualization (VT-x, VT-d) [34, Volume 3, Chapter 23], dynamic root of trust (TXT) [2], or applicative enclaves (SGX) [34, Volume 3, Chapter 36][31]. As for the BIOS, it is the most privileged piece of software executed by the hardware architecture, and implements several HSE mechanisms to remain isolated from the rest of the software stack. The correctness of these mechanisms is therefore of key importance; yet they have been the object of several compositional attacks [4, 5, 6, 7, 1]. These attacks have motivated our effort to provide a formal framework for reasoning about HSE mechanisms. However, it is important to emphasize that other mainstream architectures (*e.g.* ARM) work in a similar basis and potentially suffer similar issues. Our contributions are thus intended to be applicable to other hardware architectures.

The rest of this Chapter proceeds as follows. We provide the necessary details on how a typical x86 hardware architecture works (Section 2.1) and we explain why and how the BIOS remains isolated from the rest of the software stack at runtime (Section 2.2). This background allows us to describe the critical compositional attacks we already mentioned (Section 2.3).

#### 2.1 Introduction to x86 Architecture

Describing hardware architectures in depth is challenging, because they tend to comprise an increasing number of interconnected components of various natures. The x86 hardware architecture is a perfect illustration of this, which is probably best demonstrated by the scale

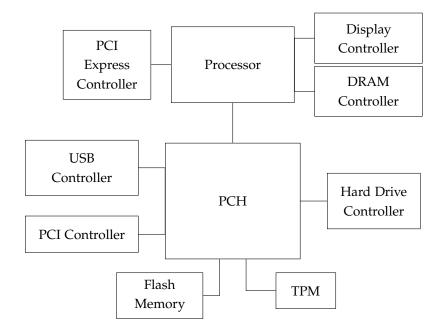

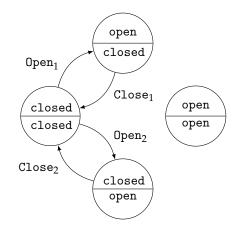

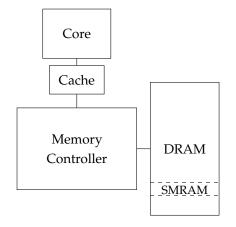

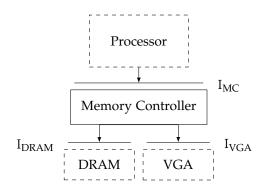

Figure 2.1: High-level view of the x86 hardware architecture

of its documentation. At the time of writing this thesis<sup>1</sup>, the *Intel 64 and IA-32 Architectures Software Developer's Manual* is 4,842 pages long. A typical computing platform is made of dozens of hardware components, including *e.g.* hard drives, a keyboard, a trackpad, an audio controller, and a graphic card. Several come with their own documentation, often in the form of large datasheets.

Figure 2.1 pictures how the most important hardware components are interconnected in a modern x86 computing platform (generation *Nehalem* [38] and newer). The two main components are the processor —responsible for executing the software stack— directly connected to high-speed peripherals (*e.g.* DRAM, a display controller), and a companion chipset called the Platform Controller which handles interactions with the rest of the peripherals (*e.g.* USB devices, hard drives). The x86 architecture has seen many iterations over the years, and it is quite common to find in the same computer park different versions of this architecture. For instance, the processor was previously connected to a *northbrige* (low-latency), which was itself connected to a *southbridge* (slower peripherals).

This section proceeds as follows. First, we describe the internals of a x86 processor (2.1.1). We detail the mechanisms which play a part in interactions between the processor and the memories scattered inside the hardware architecture (2.1.2), then focus on the caches embedded inside the processor to reduce the latency induced by these interactions (2.1.3). Finally, we explain how peripherals of the hardware platform actively communicate with the processor (2.1.4).

<sup>&</sup>lt;sup>1</sup>Spring 2018.

#### 2.1.1 Processor, Architecture and Microarchitecture.

The main component of the architecture is the *processor*. It embeds several execution units called *cores*, which are responsible for executing assembly instructions of software component programs. It also integrates several additional hardware modules to connect the cores to the rest of the hardware architecture, *e.g.* a memory controller to manage interactions with the DRAM. The concrete hardware implementation of the processor is often referred as the Intel microarchitecture, in opposition to the Intel architecture which describes the expected behavior and properties of a x86 system as seen by software developers. While Intel often modifies the microarchitecture, the architecture has remained backward compatible for decades [39]. The microarchitecture implements many optimizations, such as multithreading [40], instruction pipelining [41], out-of-order execution [41, Section 2] or predictive branching [42][41, Section 3].

Intel microarchitecture blurs the frontier between hardware and software. Indeed, an important part of the microarchitecture is not implemented as hardware circuit, but rather under the form of *microcode* programs [31, Section 2.14]. That is, the processor is a programmable device, whose behavior —including the semantics of several x86 instructions it implements [43]— is partly determined by the microcode it has loaded. In practice, x86 processors only load microcode updates which have been signed by Intel. To the best of our knowledge, x86 microcode has never been successfully used as an attack vector.

#### 2.1.2 Memories and Cores I/Os

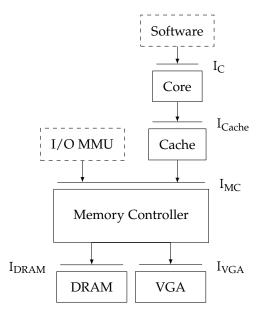

Besides cores, *memories* are the most important components of a computing platform. Cores interact with these memories during so-called I/Os, for Input/Output: a core receives data during an input and it sends data during an output. The x86 architecture integrates several sources of memories, along with several mechanisms that can be used by the cores to interact with these memories.

The main target of cores I/Os is the Dynamic Random Access Memory (DRAM). DRAM contains the instructions executed by the cores, *and* the data they manipulate. A core decides the semantics of a given memory cell depending on the context, *e.g.* the same binary sequence can be decoded as an instruction or interpreted as an operand of an arithmetic operation. In addition, other hardware components also provide additional memory regions that cores can read from or write to. Contrary to DRAM, I/Os targeting these memories often carry a semantics specific to each peripheral. For instance, an x86 processor integrates a display controller which exposes a frame buffer to the cores. By writing to the frame buffer, a core changes the pictures displayed on the computer screen.

Address Spaces. Cores interact with memories *via* two distinct memory address spaces, characterized by a set of addresses and a set of instructions. The most important address space is the *system memory*, and most of the x86 instructions (*e.g.* mov variants, arithmetic operations such as sub and add) are designed to manipulate it. Addresses of the system memory are referred to as physical addresses and the majority of system memory I/Os are dispatched to the

DRAM. Besides, cores use another address space characterized by two dedicated instructions —in and out— to target the memories exposed by other hardware components. I/Os issued by in and out instructions are referred to as Port-Mapped I/O (PMIO), and the addresses of this address space are called *ports*.

Although they are historically used to target different memory regions, nowadays these two address spaces overlap, as peripheral memories and registers can be exposed to the cores *via* the system memory thanks to *memory-mapped* I/Os. That is, *it is possible to read from or write to the same memory location using two different address spaces*. The mapping between addresses of the system memory and their concrete memory locations within the hardware architecture is called the *memory map*. This memory map is configurable, that is it can be changed dynamically *via* configuration registers exposed by the processor and the Platform Controller Hub (PCH).

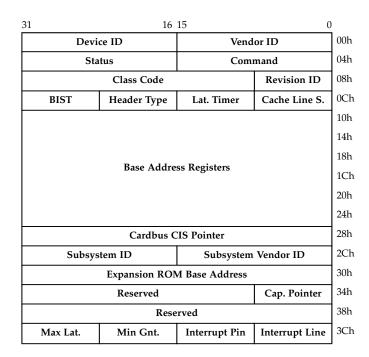

For instance, the Peripheral Component Interconnect (PCI) standard —whose aim is to propose a standard local bus and communication protocol to connect hardware components to a computing platform— introduces a so-called configuration space per PCI device, which is a dedicated memory region with a specific semantics summarized in Figure 2.2. Registers of the PCI configuration space, such as device and vendor IDs, can be accessed *via* PMIO. Indeed, the PCH exposes two ports to that end. First, software components modify the content of the PCI\_CONFIG\_ADDRESS port, to tell the PCH which PCI configuration register they want to interact with. Then, they read from and write to the PCI\_CONFIG\_DATA port, and the PCH dispatches these I/O to the targeted register. The PCI specification states that the offset 0x10 of the PCI configuration spaces is dedicated to so-called BARs (Base Address Registers). The purpose of the BARs is to configuration space of a given peripheral *via* the system memory. As a consequence, a core which reads from or write to the system memory in a range specified by a BAR sees its I/O dispatched to the configuration space of the related PCI device.

Finally, software components often do not manipulate addresses of the system memory directly. Indeed, cores have their own address translation mechanisms, namely segmentation [34, Volume 3, Section 2.4] and pagination [34, Volume 3, Chapter 4] (potentially extended with its virtualization technology [34, Volume 3, Section 28.2]), which are configurable by the software components.

As such, determining which hardware component will handle a core I/O targeting a given virtual address requires to have a complete knowledge of the x86 remapping and virtual memory mechanisms and of their exact configurations at a given time.

Access Control for Software Components. The x86 hardware architecture provides a rich collection of hardware features [34, Volume 3] to implement fine-grained access control policies about software components I/Os. Subjects of these policies include the software and hardware components of the system. Objects ultimately come down to the memory locations of various natures scattered within the hardware architecture. Actions comprise reading from and writing to a memory location. From a core perspective, it is also common to distinguish between reading data and reading instructions.

#### 2.1. INTRODUCTION TO X86 ARCHITECTURE

Figure 2.2: Standard registers of PCI Type 0 (Non-Bridge) Configuration Space Header

For instance, the MMU is probably the most well-known hardware feature to implement an access control policy. Thanks to the MMU, an operating system can attribute ranges of DRAM to user applications it manages and isolate its code and data from these applications. The MMU alone is not sufficient, because its scope does not cover its own configuration. That is, it is not possible to configure the MMU in order to prevent a software component to modify the MMU configuration. As a consequence, an additional hardware feature has to be used: the protection rings [34, Volume 3, Section 5.5]. The x86 cores can operate in 4 different so-called rings, from 0 to 3, where ring 0 is the most privileged and ring 3 the least. Ring 3 imposes several restrictions on software components, including the capability to modify the CR3 register which identifies the base of the page table hierarchy used by the MMU. This is why ring 3 is commonly dedicated to the execution of applications.

The complexity of the x86 I/O resolution mechanism requires to take into account the numerous redirection features exposed by the architecture. Memory locations can have an arbitrary number of aliases, in several layered address spaces: the DRAM controller assigns an address to each memory cell the DRAM contains; the processor maps physical addresses to DRAM addresses; the MMU maps virtual addresses to physical addresses. As a consequence, modifying the content of a memory cell may not be the only way at the disposal of attackers to defeat a given access control policy. For instance, if the access control policy refers to virtual addresses *v*, modifying the MMU configuration results in modifying the content associated with *v*.

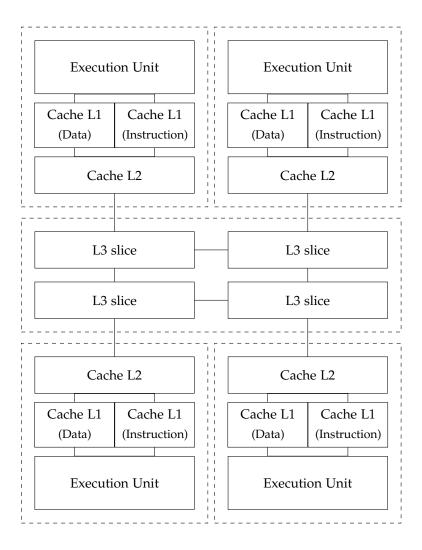

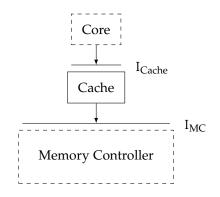

#### 2.1.3 Cache Memory

Interacting with the DRAM remains slow, in regard to the speed of cores. To improve performance, Intel processors come with several levels of caches, from the smaller and quicker, to the bigger and slower. For instance, Intel Core i7, i5 and i3 processors have three levels of caches. Each core is assigned two levels of cache called L1 —which has the particularity of being divided into a cache of instructions (used when the core read from memory instructions to execute) and a cache of data — and L2, while they all share a so-called L3 cache divided into interconnected slices. Figure 2.3 summarizes this organization.

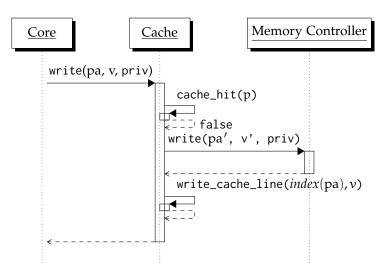

Caches are divided into several *cache blocks* addressed by an index. Cache blocks are divided into several *cache lines*, which are tagged with a memory address and contains a copy of the data stored at this address. A cache is characterized by the number of cache lines per cache block, the nature of the address associated with cache block indexes, and the nature of the address used to tag cache line. For instance, Intel L2 and L3 caches are *physically-indexed*, *physically-tagged*, meaning they use physical address to compute both the index and the tag.

Caches are mostly transparent to the software components. For instance, the processor alone enforces the cache coherence, with the notable exception of multiprocessor (not multicore) systems, for which "maintenance of cache consistency may, in rare circumstances, require intervention by system software." Intel has developed a dedicated protocol called MESIF to that end [38].

When a core successfully reads the memory at a given address, it keeps a copy of the result in its caches. Therefore, the next time it needs to read some data at this address, these data are retrieved from the cache. Regarding write accesses, Intel x86 processors provide five different caching strategies (uncacheable, write combining, write-through, write-back and write-protected) [34, Volume 3, Chapter 11]. Fine-grained cache strategy configuration is achieved through several hardware mechanisms, including (but not limited to):

- The CR0 register has a flag called CD, which enables caching once set.

- The processor has several registers called Memory Type Range Registers (MTRR), to specify a cache strategy for pre-defined memory regions.

- The Page Table Attribute (PAT) allows for configuring a cache strategy at a memory page granularity.

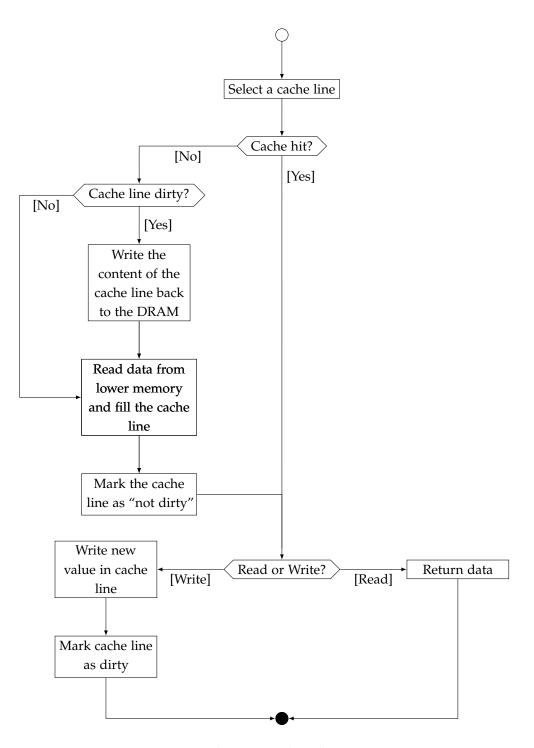

The write-back strategy is the most commonly used and is summarized in Figure 2.4. The purpose of this strategy is to reduce the number of I/O forwarded to the DRAM. To that end, each cache line has a "dirty bit" which is set by the cache when its value is updated by a write access. A *cache eviction* occurs when the cache frees a given cache line previously used for a given address in order to use it for another one. When it happens, the cache verifies the value of the "dirty bit", so it can update the underlying memory cell if necessary. Therefore, as long as the cache line is not evicted, the processor does not issue write access to the underlying memory. The write-back strategy is not suitable for memories of other hardware components

Figure 2.3: Typical caches organization of a x86 processor

mapped into the system memory. For instance, caching I/Os targeting a framebuffer does not make sense, because the screen wouldn't be updated. This is why Intel provides four complementary strategies. The uncacheable strategy disables the cache for the given address, while write combining, write-through, write-back and write-protected are similar strategies such that copies of the underlying memory are stored in the cache to accelerate read accesses, but write accesses are directly forwarded.

#### 2.1.4 Peripherals I/Os

Cores are not the only active hardware components present inside a typical x86 hardware architecture. For instance, several hardware components can also read from or write to the DRAM using a technology called Direct Memory Access (DMA). Hardware components can also interact with the processor by sending hardware interrupts of various natures. When a user presses a key of its keyboard, the latter sends an interrupt request. Interrupt handlers, that is programs executed by the core when it receives interrupts, are configurable *via* a so-called Interrupt Descriptor Table (IDT) [34, Volume 3, Chapter 6]. Each line of the IDT corresponds to a given interrupt whose semantics is specified by Intel, as summarized in Table 2.1. When a core handles an interrupt, it saves its current context inside the DRAM, then starts executing the corresponding interrupt handler. Not all x86 interrupts come from a hardware component. Cores use several of them, for instance to recover from errors. For example, if a core is not able to translate a virtual address into a physical address, it raises a so-called page fault.

Access Control for Hardware Components. Hardware components come from various places and can be of various qualities. Once integrated together, an attacker can potentially leverage any of them to threaten the security of the system. In this context, the principle of least privilege [44] applies: a given component should only be able to leverage capabilities it needs to work according to its purpose, where a "capability" refers to the right to perform a given I/O. To impose an access control policy to hardware components, a system software component uses the so-called VT-d feature, which implements an I/O-MMU for x86 computing platform [45].

In practice, the correct enforcement of an access control policy for hardware components remains challenging, for various reasons. Firstly, security checks can have an important impact on performance. Partly for this reason, the hardware components have long been assumed trustworthy. A good demonstration of this fact is the Address Translation Services mechanism introduced by the PCI standard, whose purpose is to allow PCI devices to bypass security mechanisms designed to reduce their privileges [46]. Other examples showed blind trust in foreign hardware components (*e.g.* USB devices) is not without consequences from a security perspective [47, 48, 49]. Secondly, the "least privilege" may vary from one execution to another, *e.g.* depending on the software stack executed. To handle the numerous use cases of the x86 architecture, its default configuration is very permissive, until software components such as the BIOS or an operating system modify it to fit their needs, by implementing HSE mechanisms.

Figure 2.4: The Write-Back cache strategy

| #IRQ     | Semantics                               |

|----------|-----------------------------------------|

| 0x00     | Division by zero                        |

| 0x01     | Single-step interrupt                   |

| 0x02     | Non-Maskable Interrupt (NMI)            |

| 0x03     | Breaking point (used by debuggers)      |

| 0x04     | Stack overflow                          |

| 0x05     | Bounds                                  |

| 0x06     | Invalid instruction opcode              |

| 0x07     | Coprocessor not available               |

| 0x08     | Double fault                            |

| 0x09     | Coprocessor segment overrun             |

| 0x0A     | Invalid task state segment              |

| 0x0B     | Segment not present                     |

| 0x0C     | Stack fault                             |

| 0x0D     | General protection fault                |

| 0x0E     | Page fault                              |

| 0x0F     | Reserved by Intel                       |

| 0x10     | Math fault                              |

| 0x11     | Alignment check                         |

| 0x12     | Machine check                           |

| 0x13     | SIMD floating-point exception           |

| 0x14     | Control protection exception            |

| ble 2.1: | x86 Interrupt Descriptor Table semantic |

Table 2.1: x86 Interrupt Descriptor Table semantics

#### 2.1.5 Conclusion

This introduction to the x86 hardware architecture provides the necessary background to understand the challenges related to the implementation of a HSE mechanism in general. In the next section, we explain why the BIOS requires such an isolated environment to operate, and we detailed the hardware features it leveraged to that end.

#### 2.2 **BIOS Overview**

The BIOS plays a significant role in Intel x86 computing platform. It is the first piece of software executed by the processor, which initializes the hardware components and initiates the execution of the software stack during the boot sequence (2.2.1). At runtime, it remains active to perform various tasks, including and not limited to platform-specific events, device emulation, or BIOS updates management (2.2.2). As such, it can only operate properly if certain security requirements are met and implements several HSE mechanisms to that end (2.2.3).

#### 2.2.1 During the boot sequence

The BIOS program is stored inside a small flash memory connected to the PCH through the Serial Peripheral Interface (SPI) bus on modern x86 computing platform. When the computing platform is powered up, the processor starts executing the code stored at a hardcoded address within the flash memory. The first task of the BIOS is to initialize the hardware architecture [50]. Then, the BIOS searches for a system software component to load into memory. Historically, "legacy" BIOSes were looking for a Master Boot Record (MBR) at the beginning of mass storage devices (*e.g.* hard drive, USB stick). The MBR, whose size is limited to 512 bytes, contains a small program to initiate a loader for a system software component. Modern BIOSes implement the Unified Extensible Firmware Interface (UEFI) [51, 52] standard, whose purpose is to standardize the boot sequence process in order to favor interoperability of BIOS implementations. The boot sequence is divided into several phases, and the BIOS is packaged into several software components accordingly. In particular, UEFI-compliant BIOS can load so-called UEFI applications of arbitrary size, leading modern hypervisors and operating systems to be packaged as UEFI applications [53].

Because the BIOS is the first software component executed by the hardware architecture, and is responsible for initiating the execution of following software components (*e.g.* an operating system), it is commonly designated as the root of trust[54] for the software stack. As such, the integrity of the BIOS code is critical, and several strategies have been proposed to detect BIOS code corruption during the boot sequence, with the two most predominant being Secure Boot [55] and Trusted Boot [56]. Secure Boot and Trusted Boot can uncover certain BIOS corruptions prior to the execution of the illegitimate code. However, they both rely on a so-called *root of trust*, which is the initial code of the BIOS, whose integrity cannot be guaranteed for certain because it is not stored on a read-only memory. Recent efforts have been expended to overcome this limitation. For instance, in 2013 HP has introduced a security mechanism

called SureStart [57] whose purpose is to move the root of trust within another hardware component, leaving most attackers unable to modify its code. More recently, the NIST has published the Special Communication 800-193 —*Platform Firmware Resiliency Guidelines* [58]— which specifically tackles the challenge posed by illegitimate firmware modification. These approaches have in common to aim at enforcing the correct initialization of the platform by the BIOS.

#### 2.2.2 At runtime

The boot sequence ends once a system software component has been selected and loaded into memory by the BIOS.

**Software Interfaces.** At runtime, the BIOS provides various software interfaces to the system software component. For instance, the Advanced Configuration and Power Interface (ACPI) tables [59, 60] is a standardized interface to configure various vendor-specific aspects of the hardware platform, such as power management or thermal management. Similarly, legacy BIOSes expose facilities to system software components, in the form of so-called BIOS Interrupt. For instance, the interrupt 0x10 is dedicated to video services (*e.g.* setting the video mode, setting the cursor shape and position, etc.). Nowadays, UEFI-capable BIOSes expose so-called *Runtime Services* to system software component [61, Chapter 5] under the form of a table of function pointers.

In either case, these interfaces act as an intermediary layer between a system software component and the hardware architecture. In doing so, they reduce the coupling between the software and hardware components. Sometimes, their use is optional, and BIOSes only provide them as a facility. Other are mandatory gates towards certain computing platform features, because they are related to critical mechanisms of the platform and the hardware vendors do not want to rely on a (potentially vulnerable or malicious) system software component. For instance, the BIOS takes care of its own software updates, in order to verify submitted versions prior to applying them, *e.g.* by verifying cryptographic signature or preventing the installation of older, outdated versions.

**Proactive Features.** In addition to supporting the execution of the rest of the software stack through its interfaces, the BIOS carries out several hardware-specific tasks which are not publicly documented. This includes and is not limited to handling hardware errors, checking thermal zones, adjusting cores speed, configuring hardware workarounds, and emulate complete hardware devices to the system software component [62].